Embedded Flash memory (FLASH) for category 4 devices RM0440

160/2126 RM0440 Rev 4

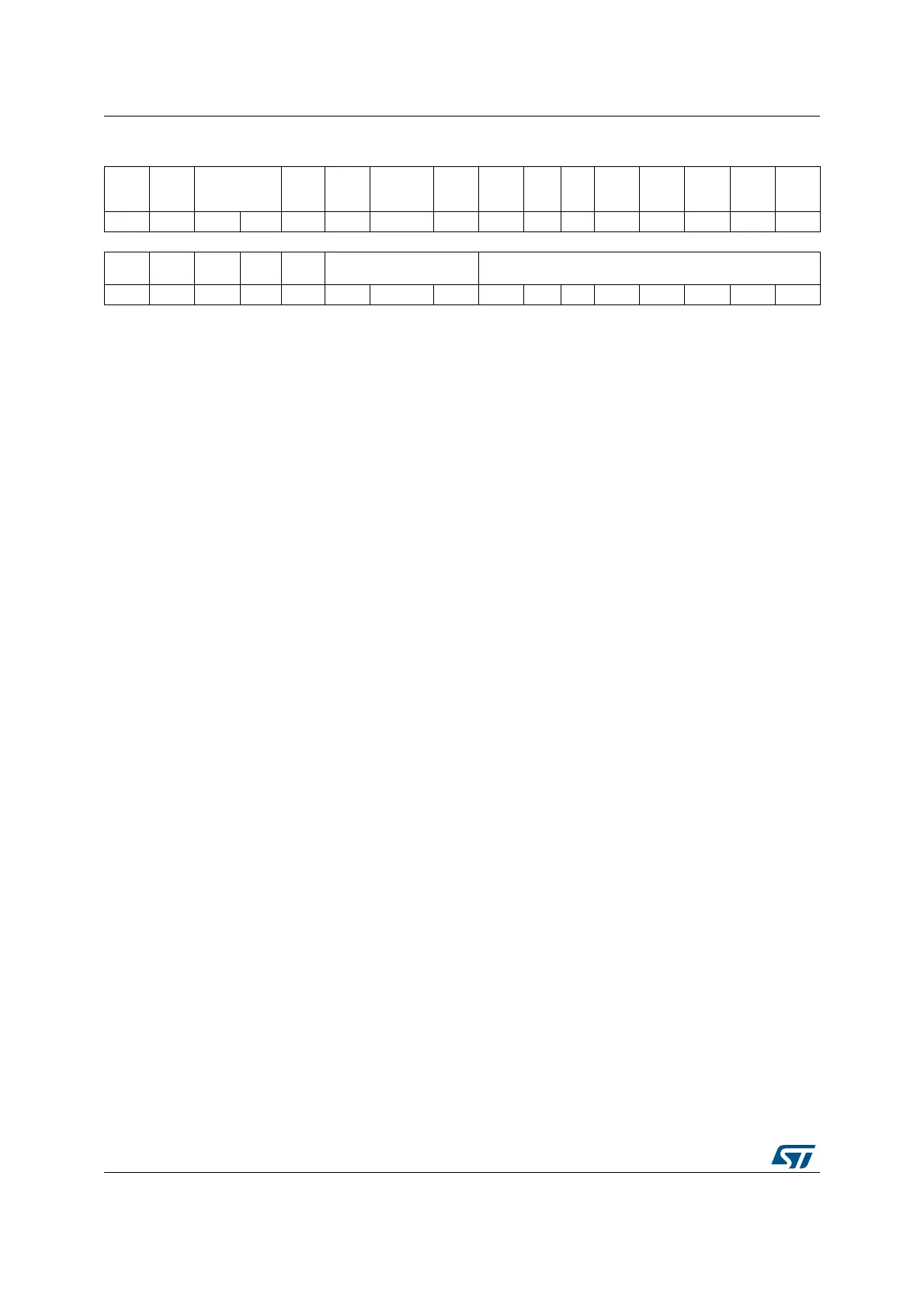

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16

Res.

IRH_

EN

PG10_

Mode

n

BOOT0

nSW

BOOT0

CCMSRAM

_RST

SRAM

_PE

n

BOOT1

PB4_

PUPE

N

Res. Res.

WWDG

_SW

IWGD_

STDBY

IWDG_

STOP

IWDG_

SW

rrr r r rrr rrrr

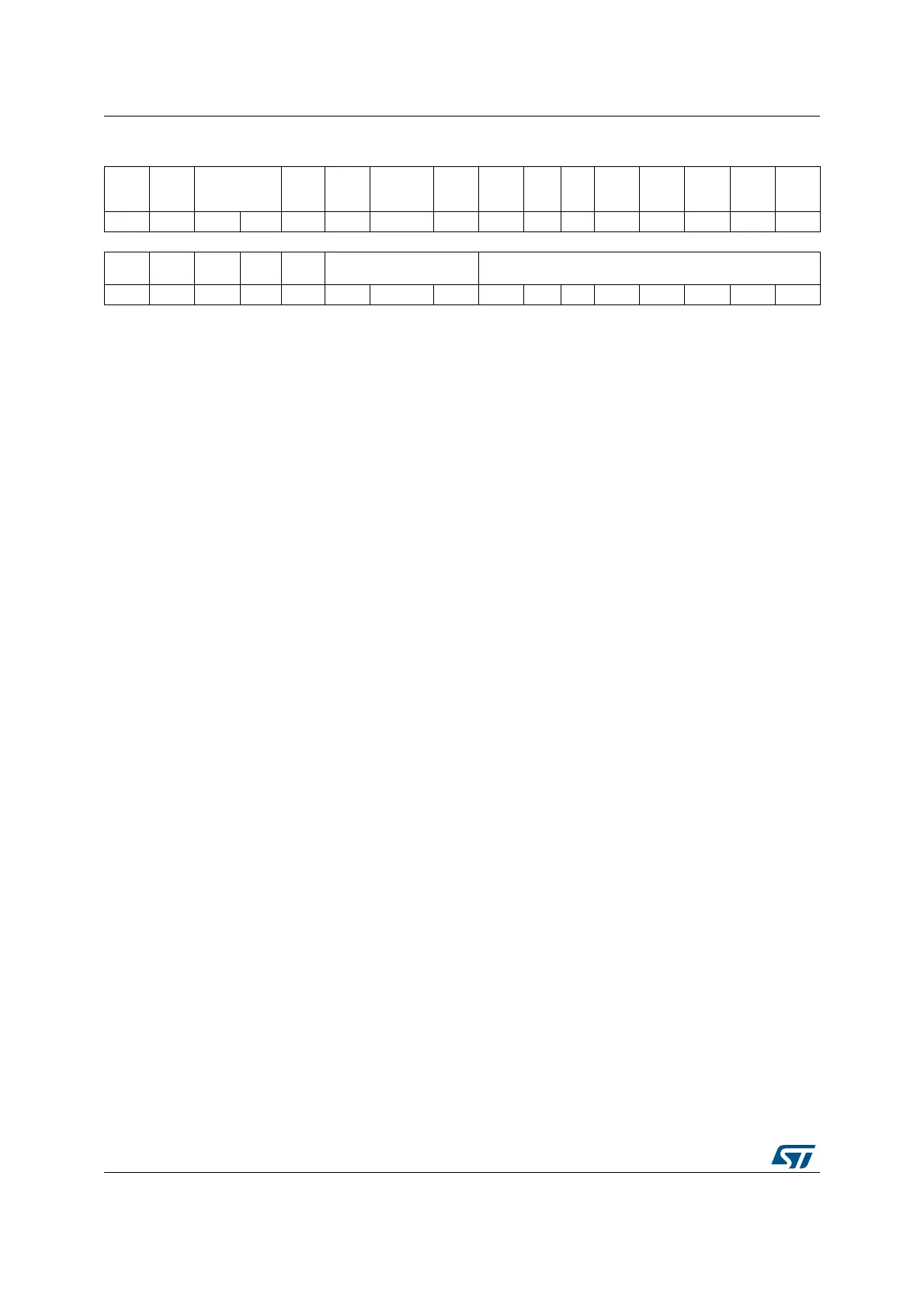

15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

Res.

nRST_

SHDW

nRST_

STDBY

nRST_

STOP

Res. BOR_LEV[2:0] RDP[7:0]

rrr r r rrrrrrrrr

Bit 31 Reserved, must be kept at reset value.

Bit 30 IRH_IN: Internal reset holder for PG10

0: IRH disabled

1: IRH enabled

Bits 29:28 PG10_Mode: PG10 pad mode

00: Reset Input/Output

01: Reset Input only

10: GPIO

11: Reset Input/Output

Bit 27 nBOOT0: nBOOT0 option bit

0: nBOOT0 = 0

1: nBOOT0 = 1

Bit 26 nSWBOOT0: Software BOOT0

0: BOOT0 taken from the option bit nBOOT0

1: BOOT0 taken from PB8/BOOT0 pin

Bit 25 CCMSRAM_RST: CCM SRAM erase when system reset

0: CCM SRAM erased when a system reset occurs

1: CCM SRAM is not erased when a system reset occurs

Bit 24 SRAM_PE: SRAM1 and CCM SRAM parity check enable

0: SRAM1 and CCM SRAM parity check enable

1: SRAM1 and CCM SRAM parity check disable

Bit 23 nBOOT1: Boot configuration

Together with the BOOT0 pin, this bit selects boot mode from the Flash main

memory, SRAM1 or the System memory. Refer to Section 2.6: Boot

configuration.

Bit 22 PB4_PUPEN: PB4 pull-up enable

0: USB power delivery dead-battery enabled/ TDI pull-up deactivated

1: USB power delivery dead-battery disabled/ TDI pull-up activated

Note: Only for Category 4 devices (otherwise Reserved)

Bits 21:20 Reserved, must be kept at reset value.

Bit 19 WWDG_SW: Window watchdog selection

0: Hardware window watchdog

1: Software window watchdog

Bit 18 IWDG_STDBY: Independent watchdog counter freeze in Standby mode

0: Independent watchdog counter is frozen in Standby mode

1: Independent watchdog counter is running in Standby mode

Loading...

Loading...