RM0440 Rev 4 1983/2126

RM0440 FD controller area network (FDCAN)

2008

44.4.12 FDCAN error counter register (FDCAN_ECR)

Address offset: 0x0040

Reset value: 0x0000 0000

44.4.13 FDCAN protocol status register (FDCAN_PSR)

Address offset: 0x0044

Reset value: 0x0000 0707

Bits 31:16 Reserved, must be kept at reset value.

Bits 15:0 TOC[15:0]: Timeout counter

The timeout counter is decremented in multiples of CAN bit times [1 … 16] depending on the

configuration of TSCC.TCP. When decremented to 0, interrupt flag IR.TOO is set and the

Timeout Counter is stopped. Start and reset/restart conditions are configured via TOCC.TOS.

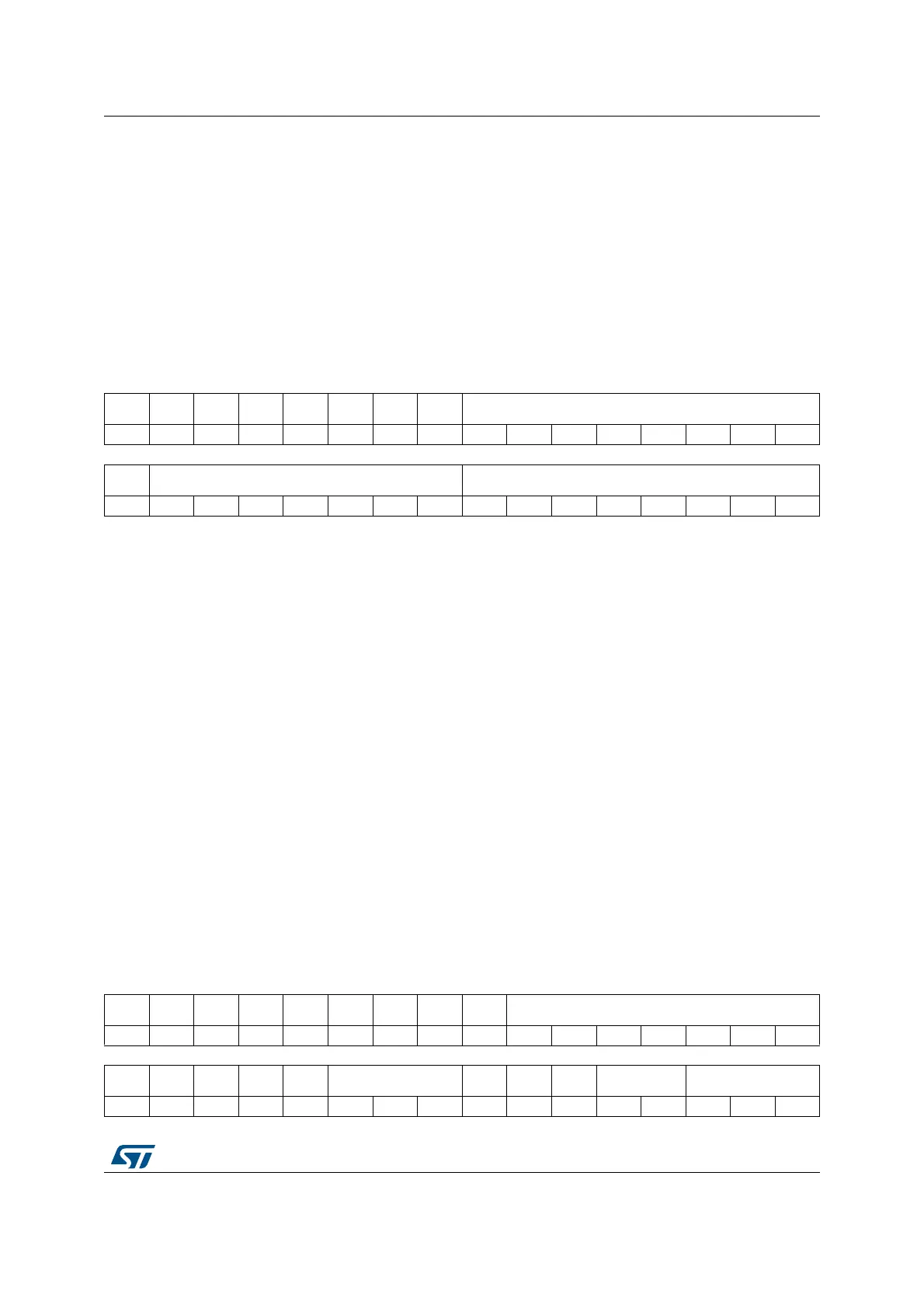

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16

Res. Res. Res. Res. Res. Res. Res. Res. CEL[7:0]

rc_r rc_r rc_r rc_r rc_r rc_r rc_r rc_r

1514131211109876543210

RP REC[6:0] TEC[7:0]

rrrrrrrrrrrrrrrr

Bits 31:24 Reserved, must be kept at reset value.

Bits 23:16 CEL[7:0]: CAN error logging

The counter is incremented each time when a CAN protocol error causes the transmit error

counter or the receive error counter to be incremented. It is reset by read access to CEL. The

counter stops at 0xFF; the next increment of TEC or REC sets interrupt flag IR[ELO].

Access type is RX: reset on read.

Bit 15 RP: Receive error passive

0: The receive error counter is below the error passive level of 128.

1: The receive error counter has reached the error passive level of 128.

Bits 14:8 REC[6:0]: Receive error counter

Actual state of the receive error counter, values between 0 and 127.

Bits 7:0 TEC[7:0]: Transmit error counter

Actual state of the transmit error counter, values between 0 and 255.

When CCCR.ASM is set, the CAN protocol controller does not increment TEC and REC

when a CAN protocol error is detected, but CEL is still incremented.

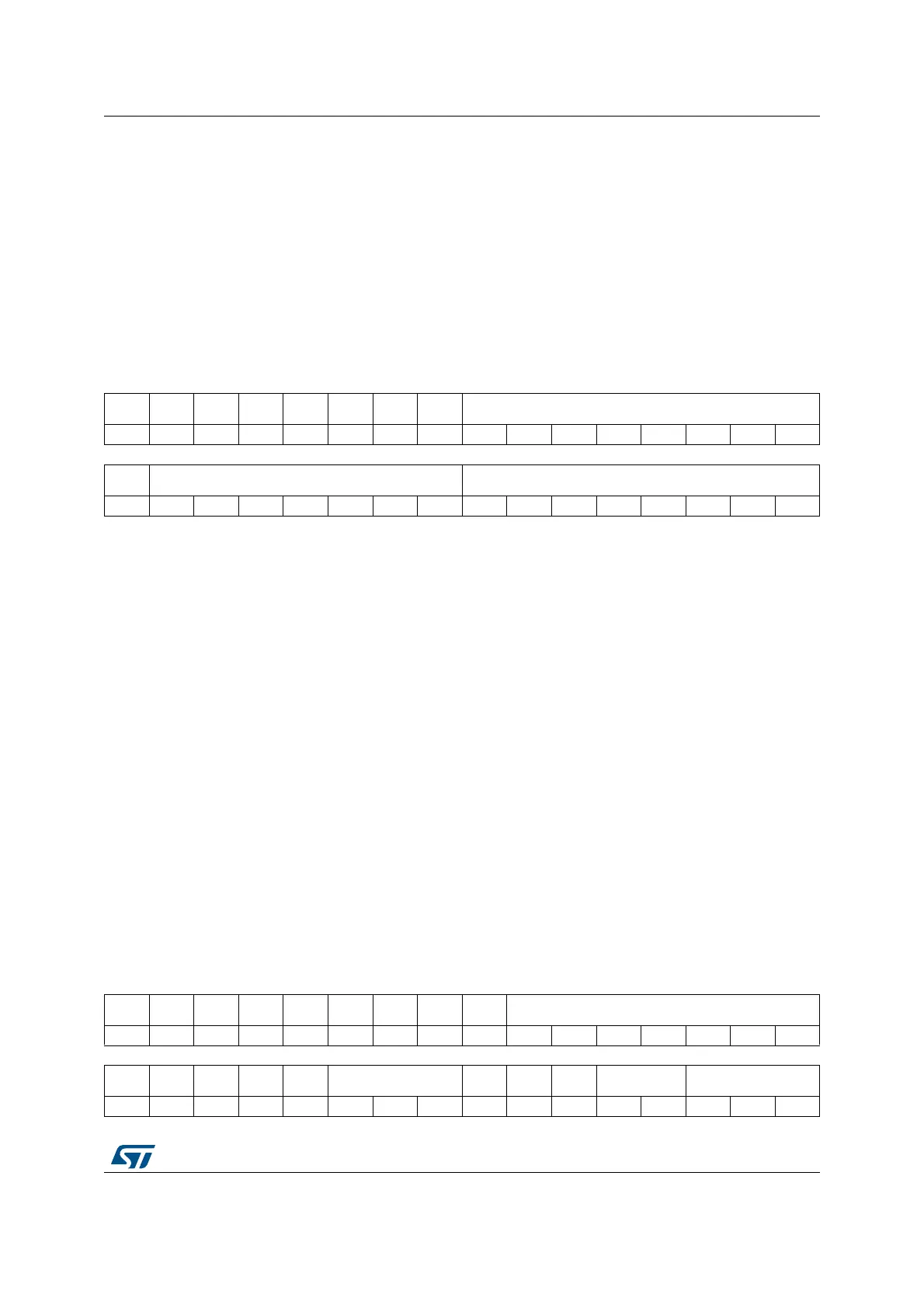

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16

Res. Res. Res. Res. Res. Res. Res. Res. Res. TDCV[6:0]

rrrrrrr

1514131211109876543210

Res. PXE REDL RBRS RESI DLEC[2:0] BO EW EP ACT[1:0] LEC[2:0]

rc_rrc_rrc_rrc_rrsrsrsrrrrrrsrsrs

Loading...

Loading...