FD controller area network (FDCAN) RM0440

1982/2126 RM0440 Rev 4

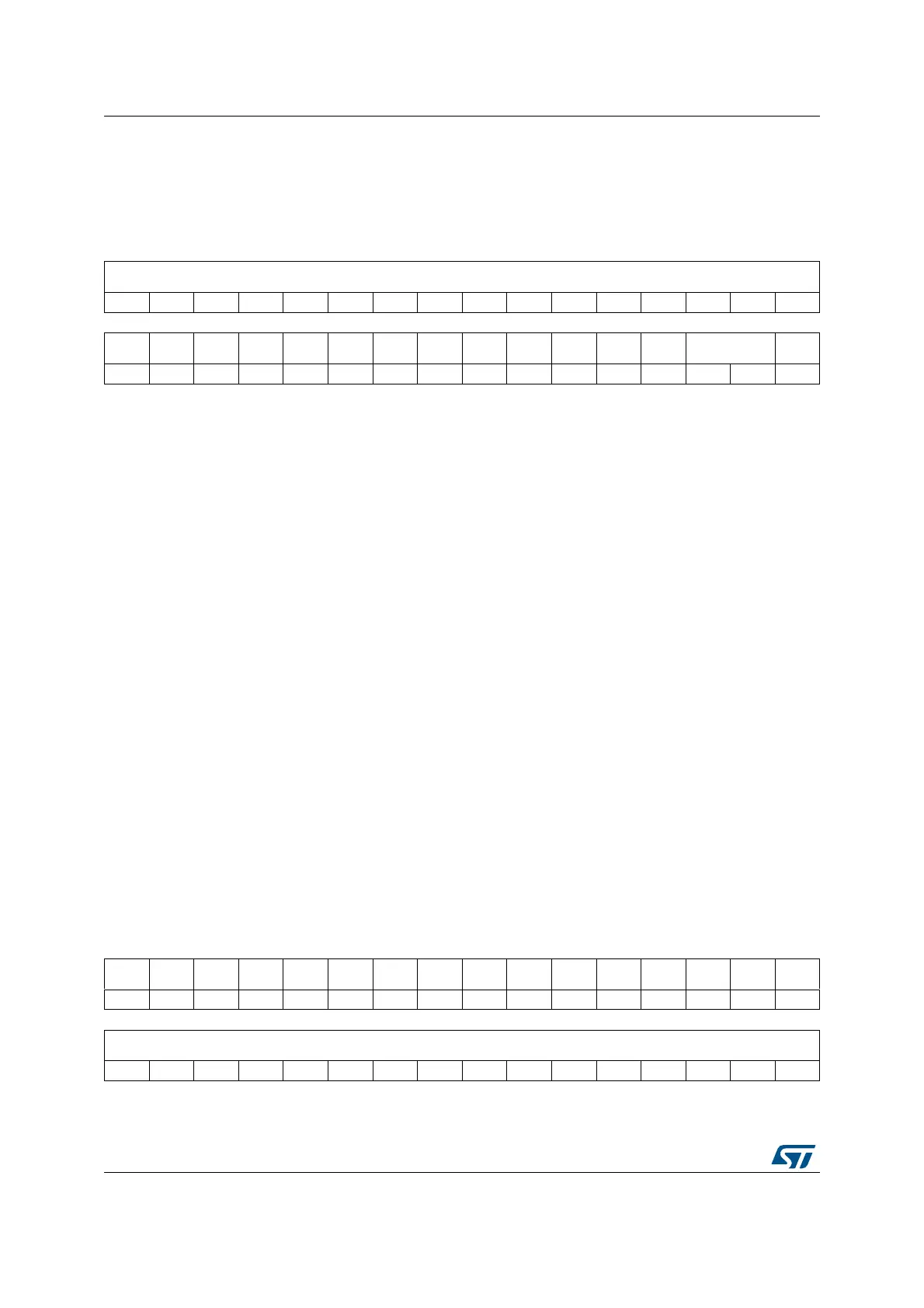

44.4.10 FDCAN timeout counter configuration register (FDCAN_TOCC)

Address offset: 0x0028

Reset value: 0xFFFF 0000

For more details see Timeout counter.

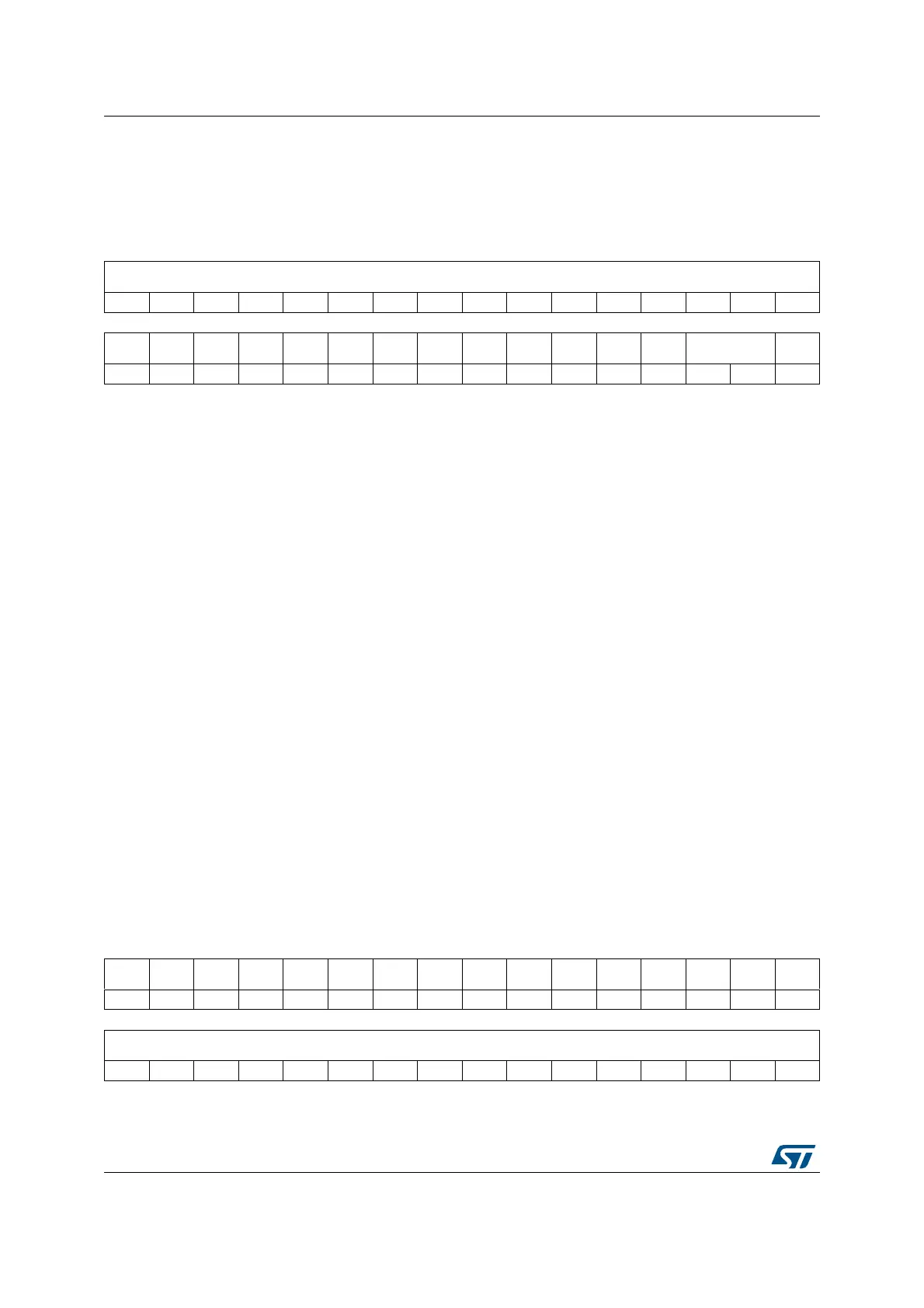

44.4.11 FDCAN timeout counter value register (FDCAN_TOCV)

Address offset: 0x002C

Reset value: 0x0000 FFFF

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16

TOP[15:0]

rw rw rw rw rw rw rw rw rw rw rw rw rw rw rw rw

1514131211109876543210

Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. TOS[1:0] ETOC

rw rw rw

Bits 31:16 TOP[15:0]: Timeout period

Start value of the timeout counter (down-counter). Configures the timeout period.

Bits 15:3 Reserved, must be kept at reset value.

Bits 2:1 TOS[1:0]: Timeout select

When operating in Continuous mode, a write to TOCV presets the counter to the value

configured by TOCC[TOP] and continues down-counting. When the timeout counter is

controlled by one of the FIFOs, an empty FIFO presets the counter to the value configured by

TOCC[TOP]. Down-counting is started when the first FIFO element is stored.

00: Continuous operation

01: Timeout controlled by Tx Event FIFO

10: Timeout controlled by Rx FIFO 0

11: Timeout controlled by Rx FIFO 1

These are protected write (P) bits, write access is possible only when the bit 1 [CCE] and bit 0

[INIT] of CCCR register are set to 1.

Bit 0 ETOC: Timeout counter enable

0: Timeout counter disabled

1: Timeout counter enabled

This is a protected write (P) bit, write access is possible only when the bit 1 [CCE] and bit 0

[INIT] of CCCR register are set to 1.

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16

Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res.

1514131211109876543210

TOC[15:0]

rc_w rc_w rc_w rc_w rc_w rc_w rc_w rc_w rc_w rc_w rc_w rc_w rc_w rc_w rc_w rc_w

Loading...

Loading...