RM0440 Rev 4 2065/2126

RM0440 USB Type-C™ / USB Power Delivery interface (UCPD)

2079

46.7.3 UCPD control register (UCPD_CR)

Address offset: 0x00C

Reset value: 0x0000 0000

Writing to this register is only effective when the peripheral is enabled (UCPDEN = 1).

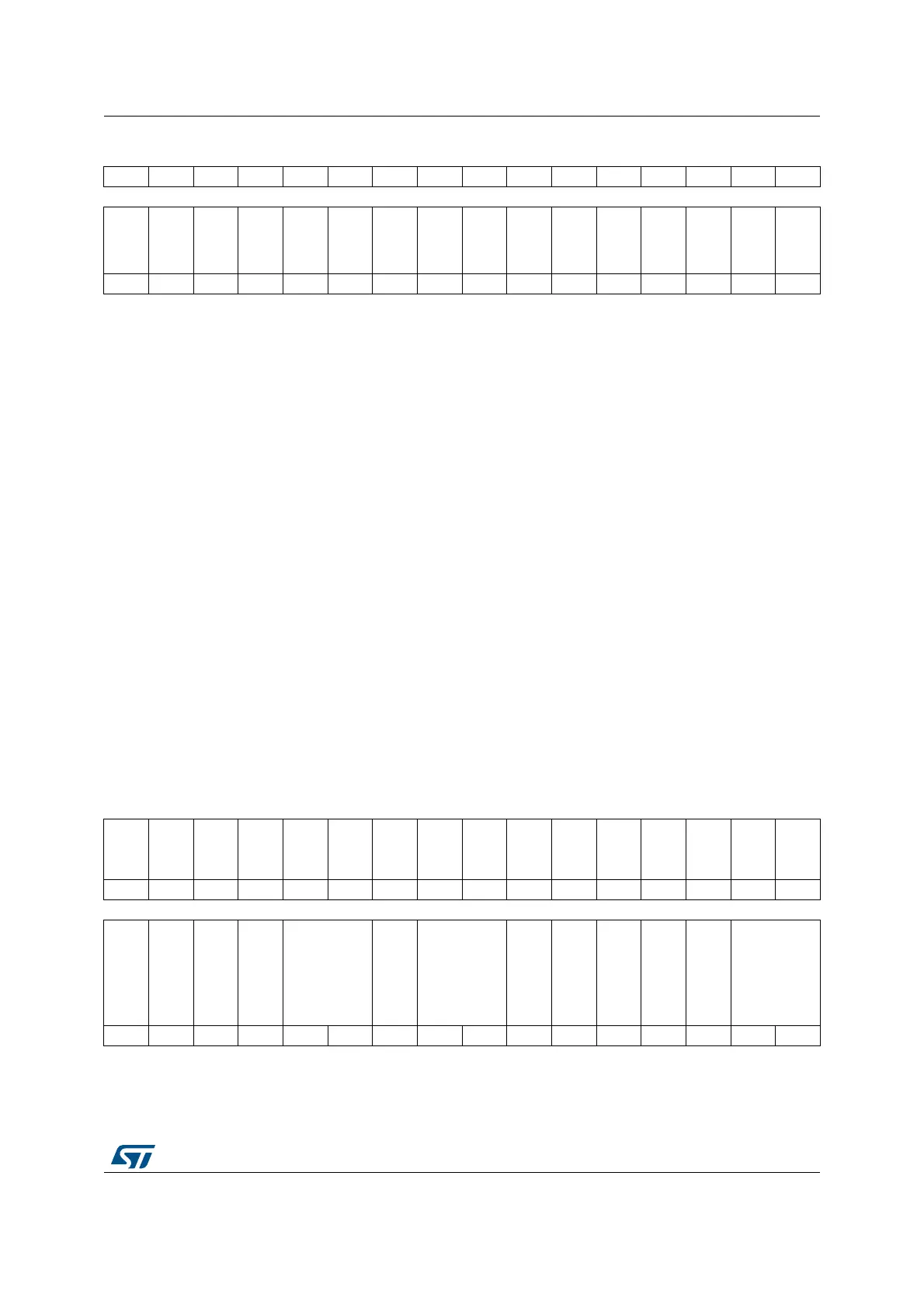

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16

Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res.

1514131211109876543210

Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res.

WUPEN

FORCECLK

RXFILT2N3

RXFILTDIS

rw rw rw rw

Bits 31:4 Reserved, must be kept at reset value.

Bit 3 WUPEN: Wakeup from Stop mode enable

Setting the bit enables the UCPD_ASYNC_INT signal.

0: Disable

1: Enable

Bit 2 FORCECLK: Force ClkReq clock request

0: Do not force clock request

1: Force clock request

Bit 1 RXFILT2N3: BMC decoder Rx pre-filter sampling method

Number of consistent consecutive samples before confirming a new value.

0: 3 samples

1: 2 samples

Bit 0 RXFILTDIS: BMC decoder Rx pre-filter enable

0: Enable

1: Disable

The sampling clock is that of the receiver (that is, after pre-scaler).

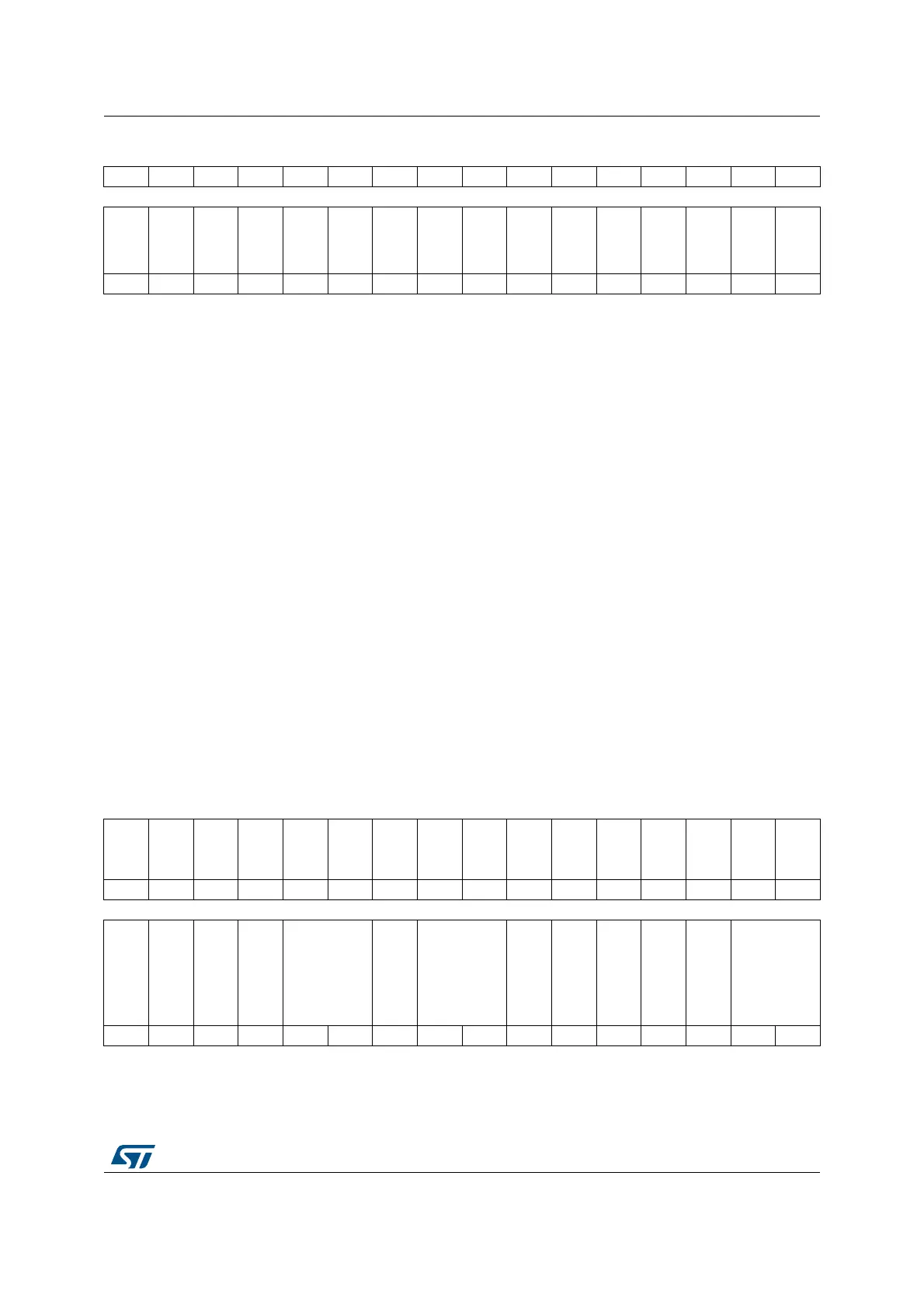

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16

Res.RE Res. Res. Res. Res. Res. Res. Res. Res. Res.

CC2TCDIS

CC1TCDIS

Res.

RDCH

FRSTX

FRSRXEN

rw rw rw rs rw

1514131211109876543210

Res.

Res.

Res.

Res.

CCENABLE[1:0]

ANAMODE

ANASUBMODE[1:0]

PHYCCSEL

PHYRXEN

RXMODE

TXHRST

TXSEND

TXMODE[1:0]

rw rw rw rw rw rw rw rw rs rs rw rw

Loading...

Loading...