RM0440 Rev 4 813/2126

RM0440 Operational amplifiers (OPAMP)

829

25.5.6 OPAMP6 control/status register (OPAMP6_CSR)

Address offset: 0x14

Reset value: 0x0000 0000

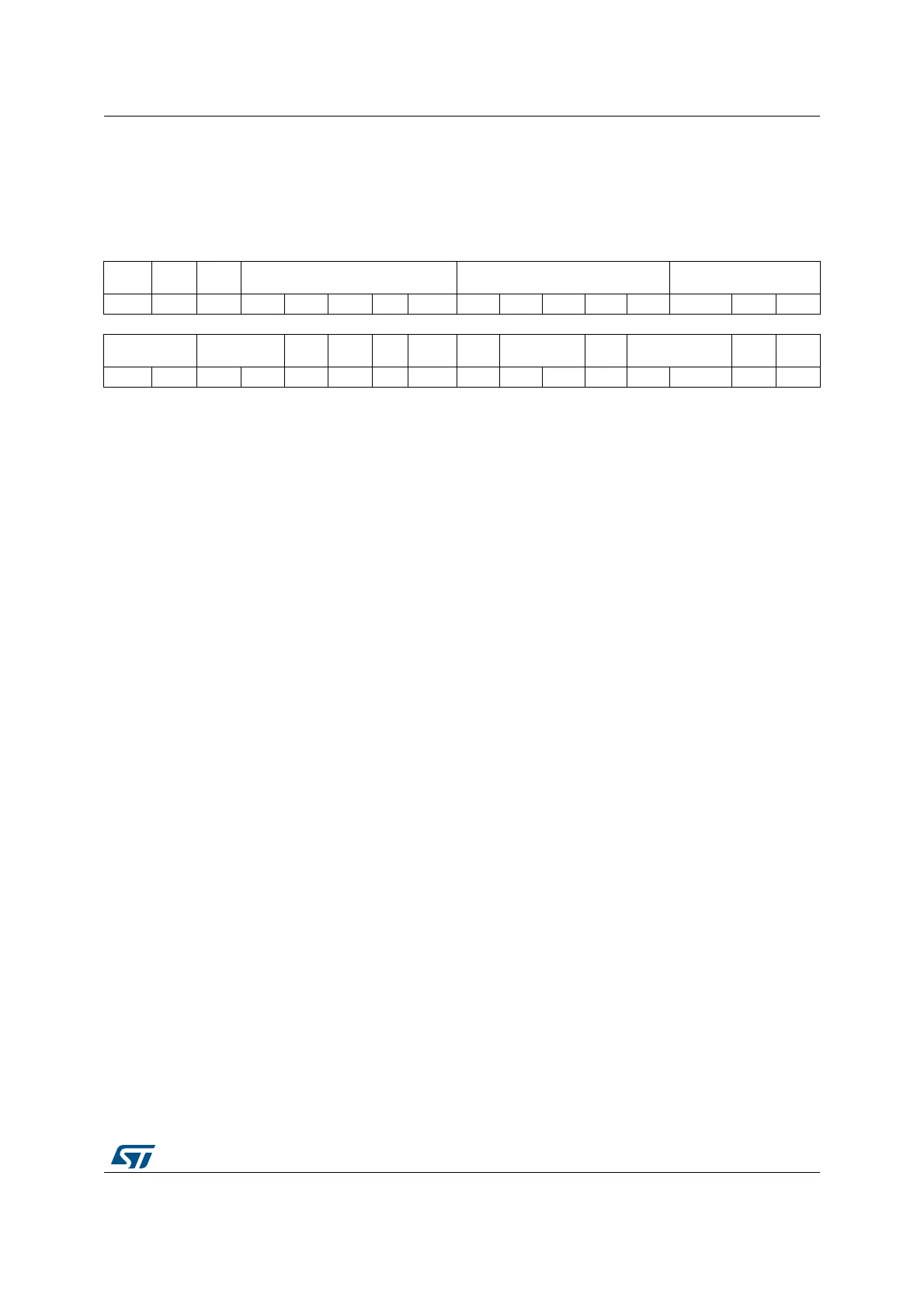

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16

LOCK

CAL

OUT

Res. TRIMOFFSETN TRIMOFFSETP PGA_GAIN

rw r rwrw rwrwrw rwrwrwrwrw rw rw rw

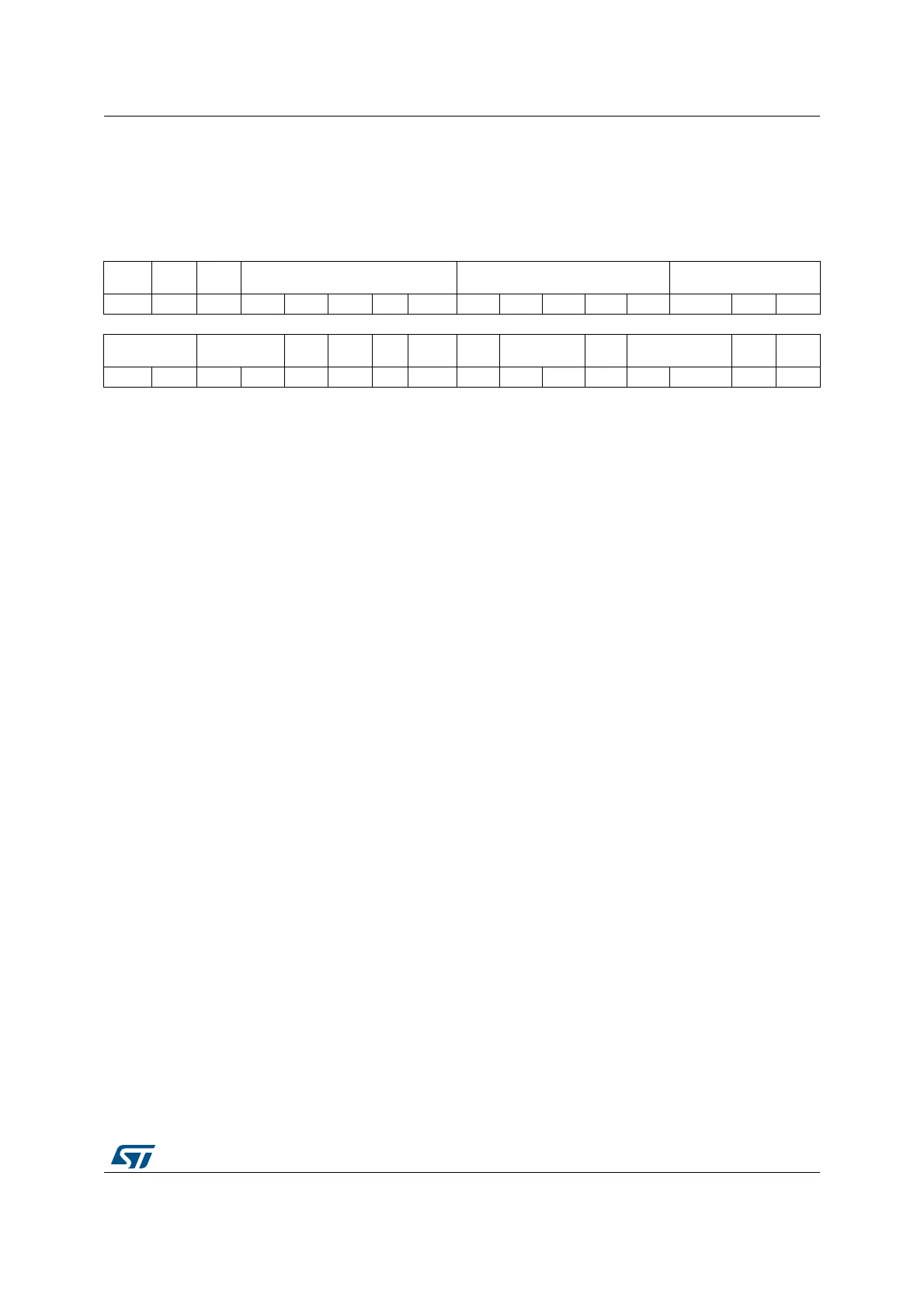

15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

PGA_GAIN CALSEL CALON Res. Res.

OPA

INTOEN

OPA

HSM

VM_SEL

USER

TRIM.

VP_SEL

FORCE

_VP

OPAEN

rw rw rw rw rw rw rw rw rw rw rw rw rw

Bit 31 LOCK: OPAMP6_CSR lock

This bit is write-once. It is set by software. It can only be cleared by a system reset.

This bit is used to configure the OPAMP6_CSR register as read-only.

0: OPAMP6_CSR is read-write

1: OPAMP6_CSR is read-only

Bit 30 CALOUT: Operational amplifier calibration output

This bit shows the digital value of OPAMP output and is the calibration output status during

calibration offset mode (Calibration is successful when CALOUT switches from 1 to 0.)

Bit 29 Reserved, must be kept at reset value.

Bits 28:24 TRIMOFFSETN [4:0]: Trim for NMOS differential pairs

Bits 23:19 TRIMOFFSETP [4:0]: Trim for PMOS differential pairs

At reset these bits are loaded by the factory trimming value. They can be modified only when

USER_TRIM =1

Loading...

Loading...