High-resolution timer (HRTIM) RM0440

978/2126 RM0440 Rev 4

27.5.15 HRTIM timer x DMA interrupt enable register (HRTIM_TIMxDIER)

(x = A to F)

Address offset: Block A: 0x08C

Address offset: Block B: 0x10C

Address offset: Block C: 0x18C

Address offset: Block D: 0x20C

Address offset: Block E: 0x28C

Address offset: Block F: 0x30C

Reset value: 0x0000 0000

Bit 7 CPT1C: Capture 1 interrupt flag clear

Writing 1 to this bit clears the CPT1 flag in HRTIM_TIMxISR register

Bit 6 UPDC: Update interrupt flag clear

Writing 1 to this bit clears the UPD flag in HRTIM_TIMxISR register

Bit 5 Reserved, must be kept at reset value.

Bit 4 REPC: Repetition interrupt flag clear

Writing 1 to this bit clears the REP flag in HRTIM_TIMxISR register

Bit 3 CMP4C: Compare 4 interrupt flag clear

Writing 1 to this bit clears the CMP4 flag in HRTIM_TIMxISR register

Bit 2 CMP3C: Compare 3 interrupt flag clear

Writing 1 to this bit clears the CMP3 flag in HRTIM_TIMxISR register

Bit 1 CMP2C: Compare 2 interrupt flag clear

Writing 1 to this bit clears the CMP2 flag in HRTIM_TIMxISR register

Bit 0 CMP1C: Compare 1 interrupt flag clear

Writing 1 to this bit clears the CMP1 flag in HRTIM_TIMxISR register

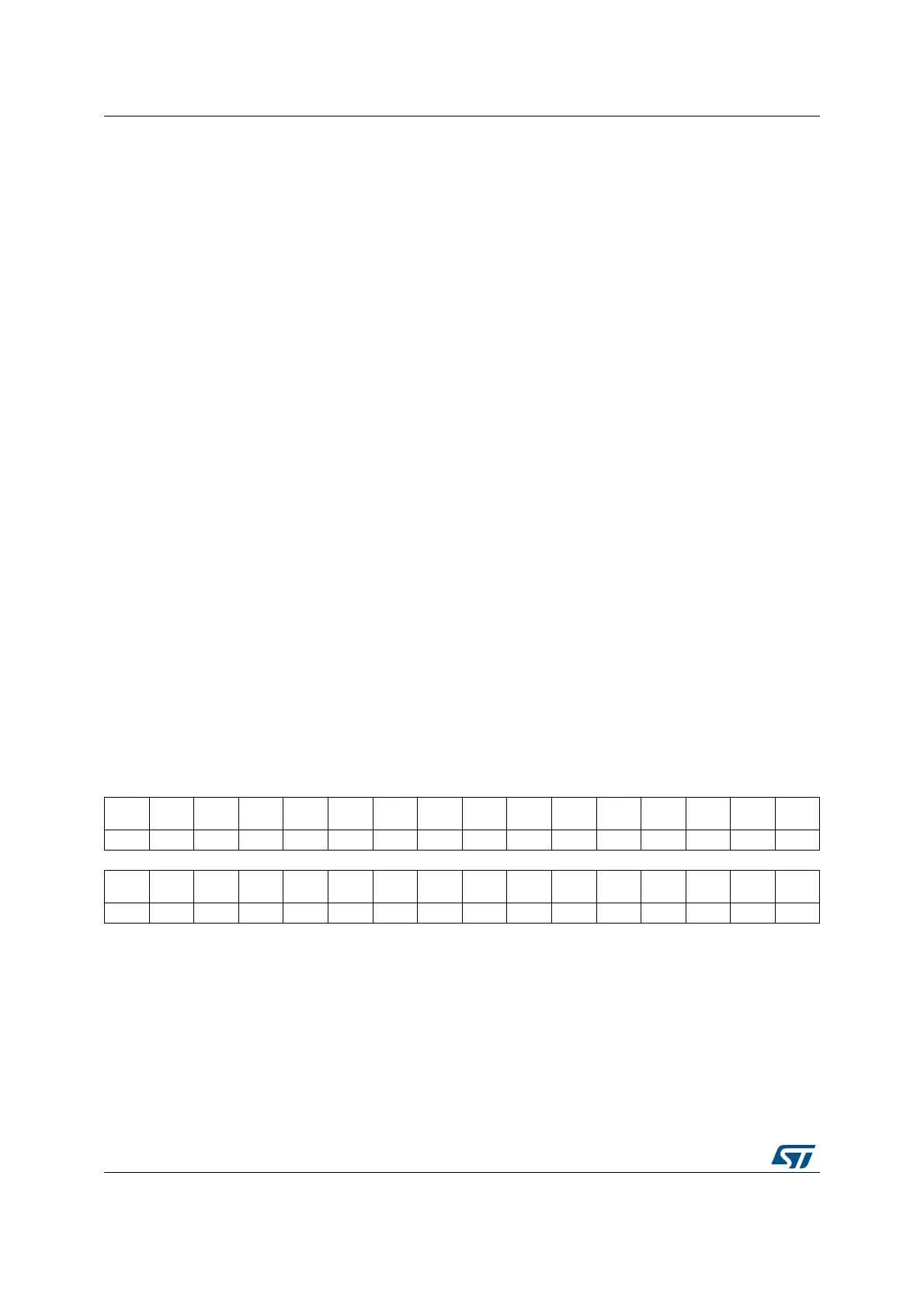

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16

Res.

DLYPR

TDE

RSTDE

RSTx2

DE

SETx2

DE

RSTx1

DE

SETx1

DE

CPT2D

E

CPT1D

E

UPDDE Res. REPDE

CMP4D

E

CMP3D

E

CMP2D

E

CMP1D

E

rw rw rw rw rw rw rw rw rw rw rw rw rw rw

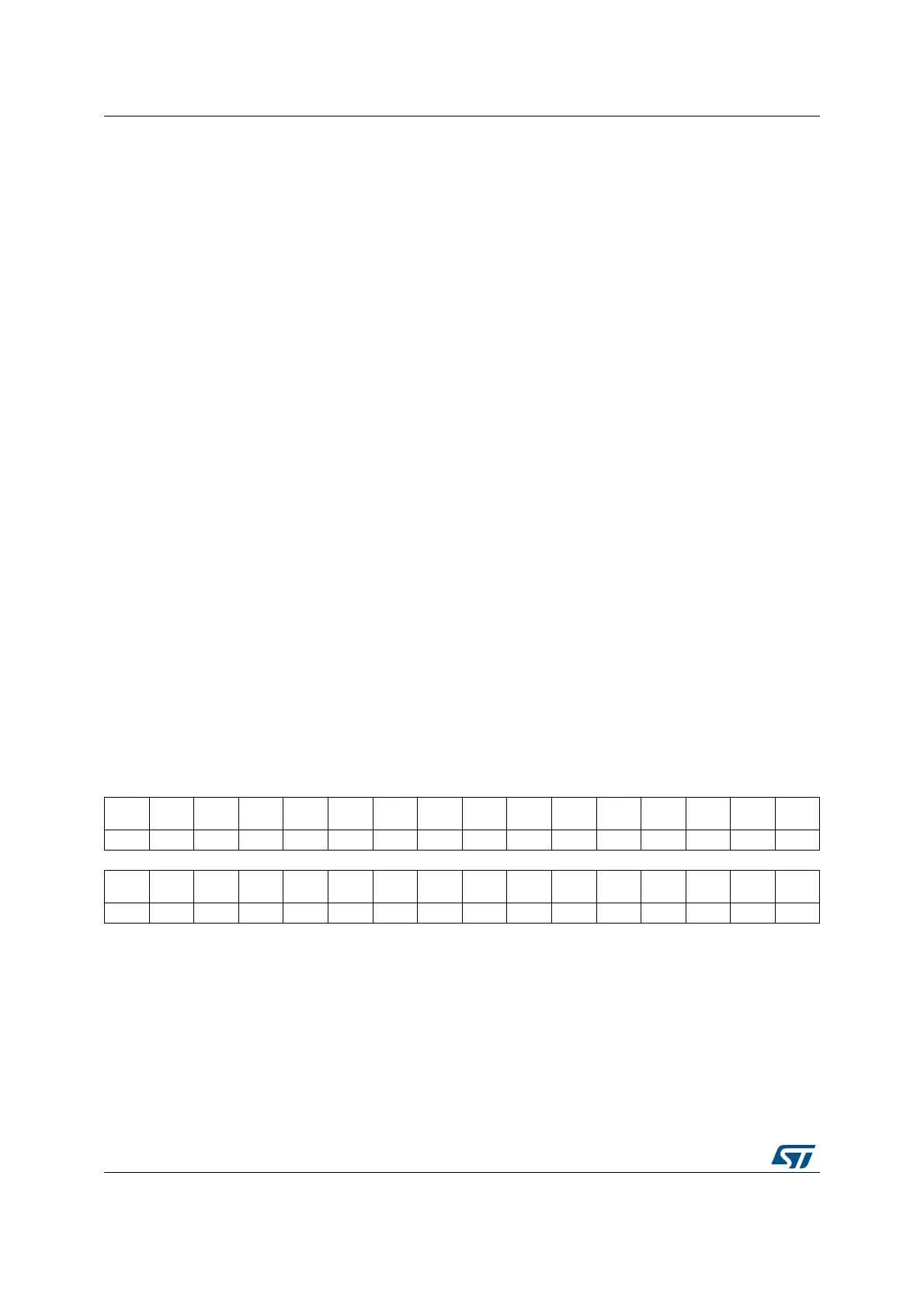

1514131211109876543210

Res.

DLYPR

TIE

RSTIE

RSTx2I

E

SETx2I

E

RSTx1I

E

SET1xI

E

CPT2IE CPT1IE UPDIE Res. REPIE

CMP4I

E

CMP3I

E

CMP2I

E

CMP1I

E

rw rw rw rw rw rw rw rw rw rw rw rw rw rw

Loading...

Loading...