High-resolution timer (HRTIM) RM0440

1034/2126 RM0440 Rev 4

27.5.53 HRTIM interrupt status register (HRTIM_ISR)

Address offset: 0x388

Reset value: 0x0000 0000

Bit 10 TBRST: Timer B counter software reset

Refer to TARST description.

Bit 9 TARST: Timer A counter software reset

Setting this bit resets the timer A counter.

The bit is automatically reset by hardware.

Bit 8 MRST: Master counter software reset

Setting this bit resets the master timer counter.

The bit is automatically reset by hardware.

Bit 7 Reserved, must be kept at reset value.

Bit 6 TFSWU: Timer F software update

Refer to TASWU description.

Bit 5 TESWU: Timer E software update

Refer to TASWU description.

Bit 4 TDSWU: Timer D software update

Refer to TASWU description.

Bit 3 TCSWU: Timer C software update

Refer to TASWU description.

Bit 2 TBSWU: Timer B software update

Refer to TASWU description.

Bit 1 TASWU: Timer A software update

This bit is set by software and automatically reset by hardware. It forces an immediate transfer from

the preload to the active register and any pending update request is canceled.

Bit 0 MSWU: Master timer software update

This bit is set by software and automatically reset by hardware. It forces an immediate transfer from

the preload to the active register in the master timer and any pending update request is canceled.

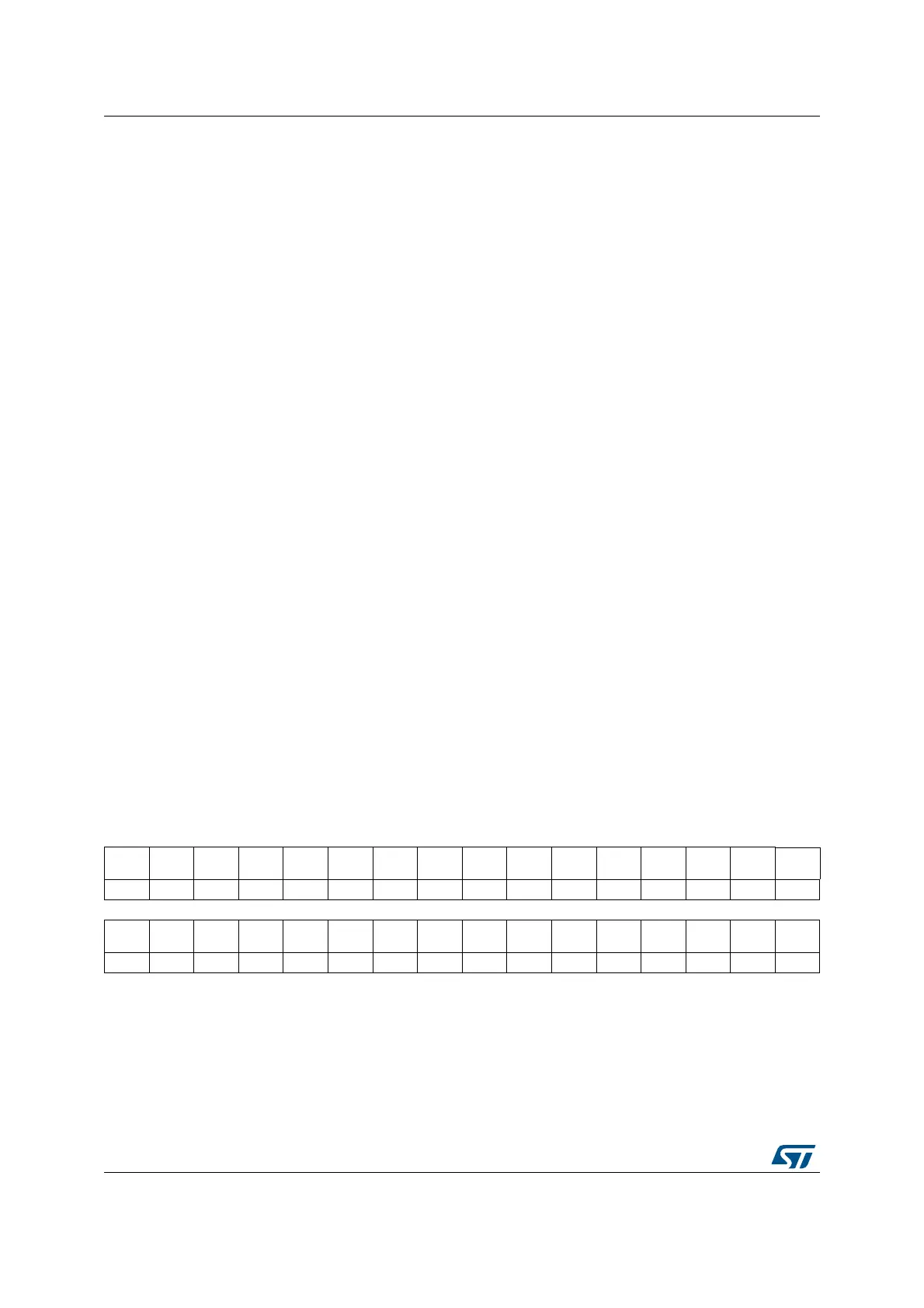

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16

Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res.

BMPE

R

DLL

RDY

rr

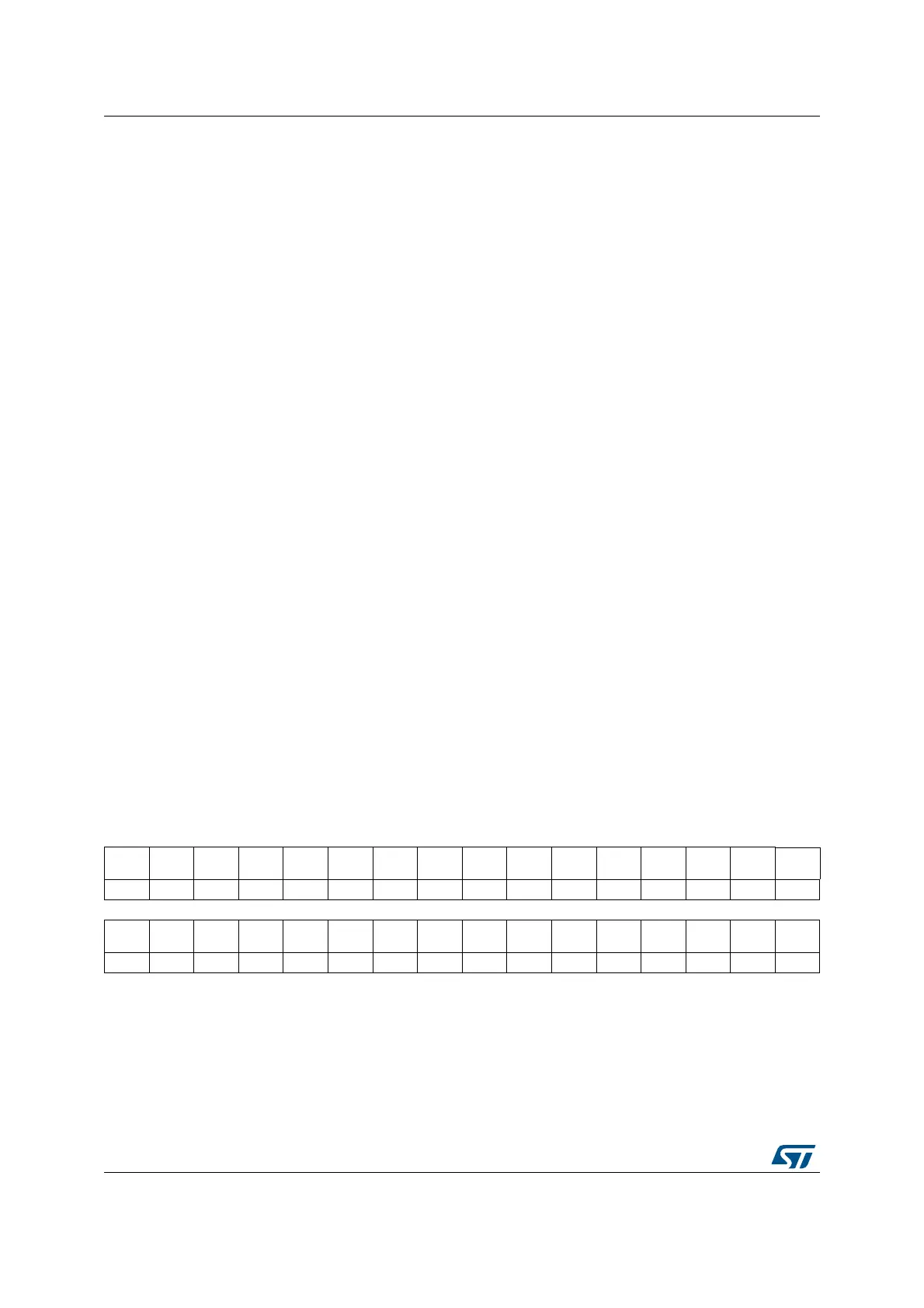

1514131211109876543210

Res. Res. Res. Res. Res. Res. Res. Res. Res. FLT6

SYSFL

T

FLT5 FLT4 FLT3 FLT2 FLT1

r rrrrr

Loading...

Loading...