High-resolution timer (HRTIM) RM0440

1038/2126 RM0440 Rev 4

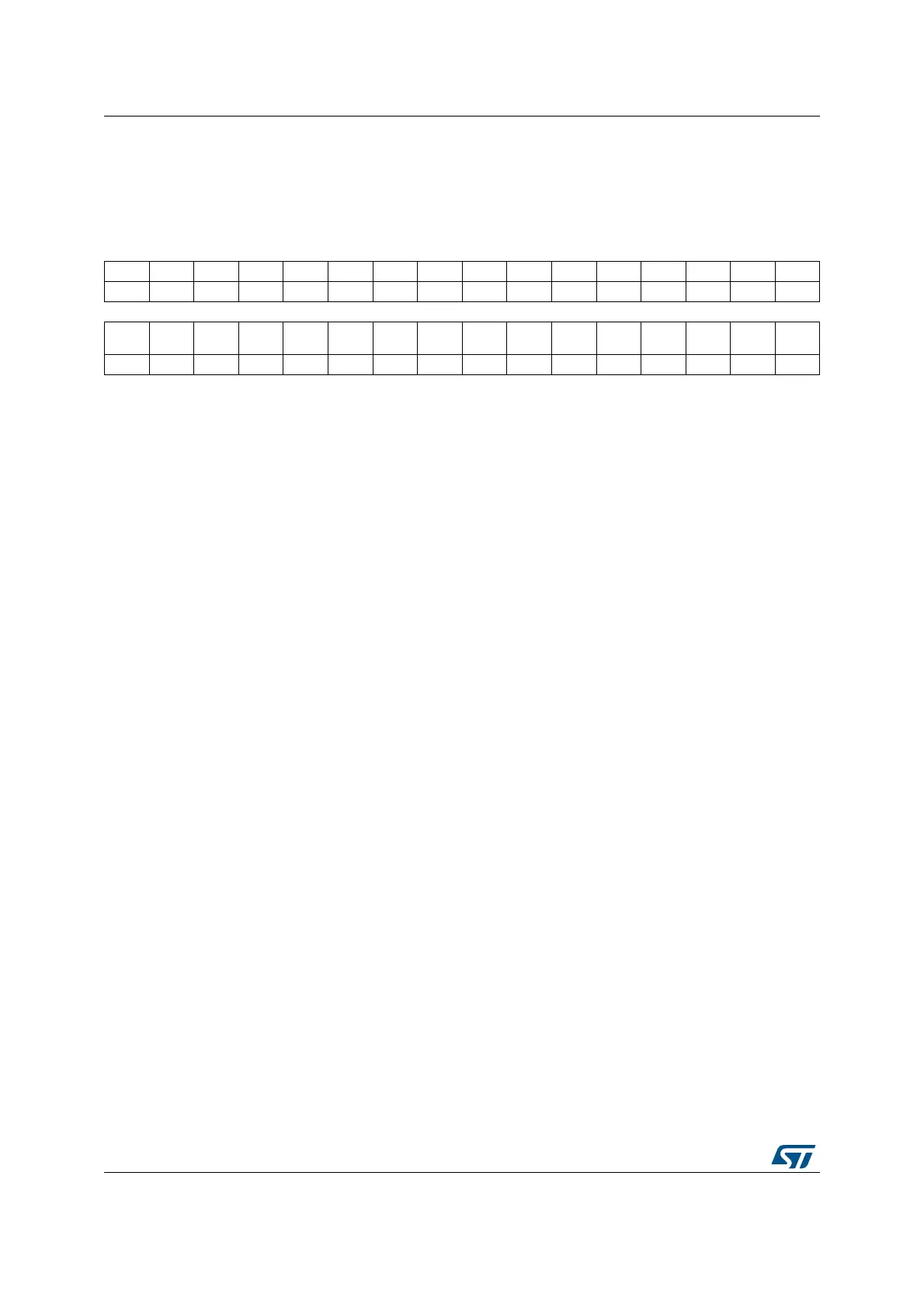

27.5.56 HRTIM output enable register (HRTIM_OENR)

Address offset: 0x394

Reset value: 0x0000 0000

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16

Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res.

1514131211109876543210

Res. Res. Res. Res.

TF2O

EN

TF1O

EN

TE2O

EN

TE1O

EN

TD2O

EN

TD1O

EN

TC2O

EN

TC1O

EN

TB2O

EN

TB1O

EN

TA2O

EN

TA1O

EN

rs rs rs rs rs rs rs rs rs rs rs rs

Bits 31:12 Reserved, must be kept at reset value.

Bit 11 TF2OEN: Timer F output 2 enable

Refer to TA1OEN description.

Bit 10 TF1OEN: Timer F output 1 enable

Refer to TA1OEN description

Bit 9 TE2OEN: Timer E output 2 enable

Refer to TA1OEN description.

Bit 8 TE1OEN: Timer E output 1 enable

Refer to TA1OEN description.

Bit 7 TD2OEN: Timer D output 2 enable

Refer to TA1OEN description.

Bit 6 TD1OEN: Timer D output 1 enable

Refer to TA1OEN description.

Bit 5 TC2OEN: Timer C output 2 enable

Refer to TA1OEN description.

Bit 4 TC1OEN: Timer C output 1 enable

Refer to TA1OEN description.

Bit 3 TB2OEN: Timer B output 2 enable

Refer to TA1OEN description.

Bit 2 TB1OEN: Timer B output 1 enable

Refer to TA1OEN description.

Bit 1 TA2OEN: Timer A output 2 enable

Refer to TA1OEN description.

Bit 0 TA1OEN: Timer A output 1 enable

Setting this bit enables the timer A output 1. Writing “0” has no effect.

Reading the bit returns the output enable/disable status.

This bit is cleared asynchronously by hardware as soon as the timer-related fault input(s) is (are)

active.

0: output A1 disabled. The output is either in fault or Idle state.

1: output A1 enabled

Note: The disable status corresponds to both idle and fault states. The output disable status is given

by TA1ODS bit in the HRTIM_ODSR register.

Loading...

Loading...