RM0440 Rev 4 1061/2126

RM0440 High-resolution timer (HRTIM)

1083

27.5.73 HRTIM burst DMA master timer update register (HRTIM_BDMUPR)

Address offset: 0x3D8

Reset value: 0x0000 0000

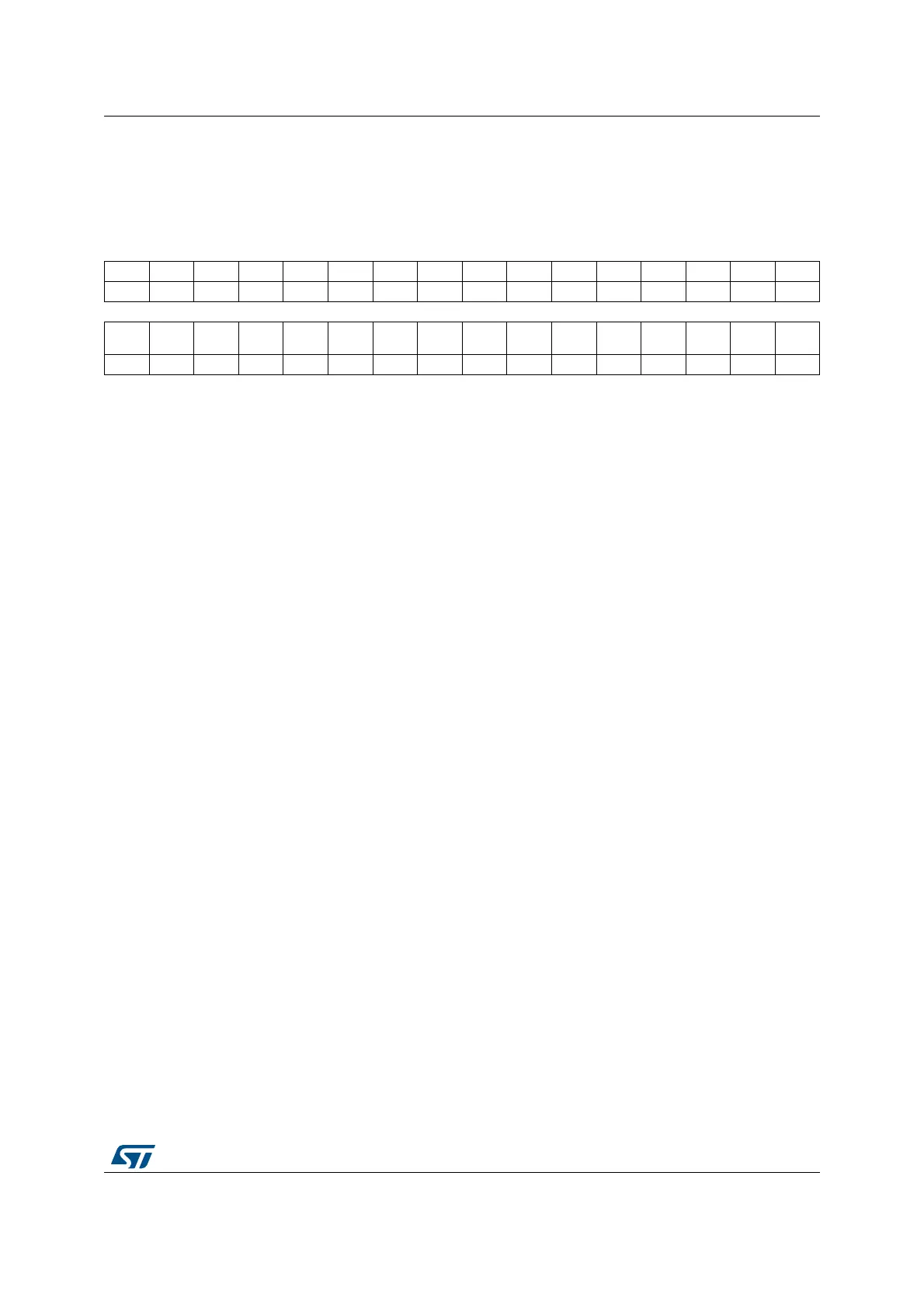

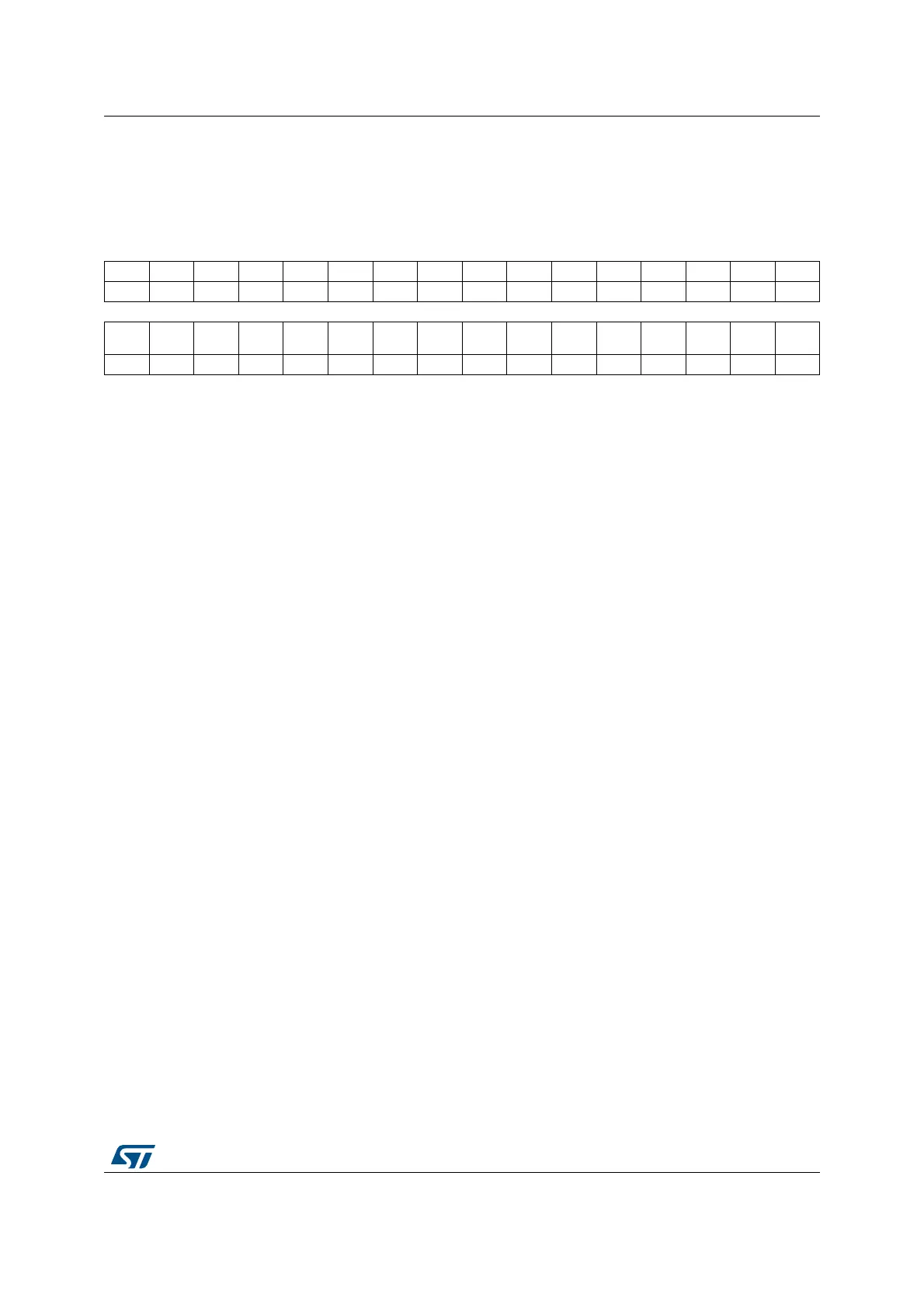

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16

Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res.

1514131211109876543210

Res. Res. Res. Res. Res. Res.

MCMP

4

MCMP

3

MCMP

2

MCMP

1

MREP MPER MCNT MDIER MICR MCR

rw rw rw rw rw rw rw rw rw rw

Bits 31:10 Reserved, must be kept at reset value.

Bit 9 MCMP4: MCMP4R register update enable

Refer to MCR description.

Bit 8 MCMP3: MCMP3R register update enable

Refer to MCR description.

Bit 7 MCMP2: MCMP2R register update enable

Refer to MCR description.

Bit 6 MCMP1: MCMP1R register update enable

Refer to MCR description.

Bit 5 MREP: MREP register update enable

Refer to MCR description.

Bit 4 MPER: MPER register update enable

Refer to MCR description.

Bit 3 MCNT: MCNTR register update enable

Refer to MCR description.

Bit 2 MDIER: MDIER register update enable

Refer to MCR description.

Bit 1 MICR: MICR register update enable

Refer to MCR description.

Bit 0 MCR: MCR register update enable

This bit defines if the master timer MCR register is part of the list of registers to be updated by the

burst DMA.

0: MCR register is not updated by burst DMA accesses

1: MCR register is updated by burst DMA accesses

Loading...

Loading...