High-resolution timer (HRTIM) RM0440

1062/2126 RM0440 Rev 4

27.5.74 HRTIM burst DMA timer x update register (HRTIM_BDTxUPR)

(x = A to F)

Address offset: Block A: 0x3DC

Address offset: Block B: 0x3E0

Address offset: Block C: 0x3E4

Address offset: Block D: 0x3E8

Address offset: Block E: 0x3EC

Address offset: Block F: 0x3F4

Reset value: 0x0000 0000

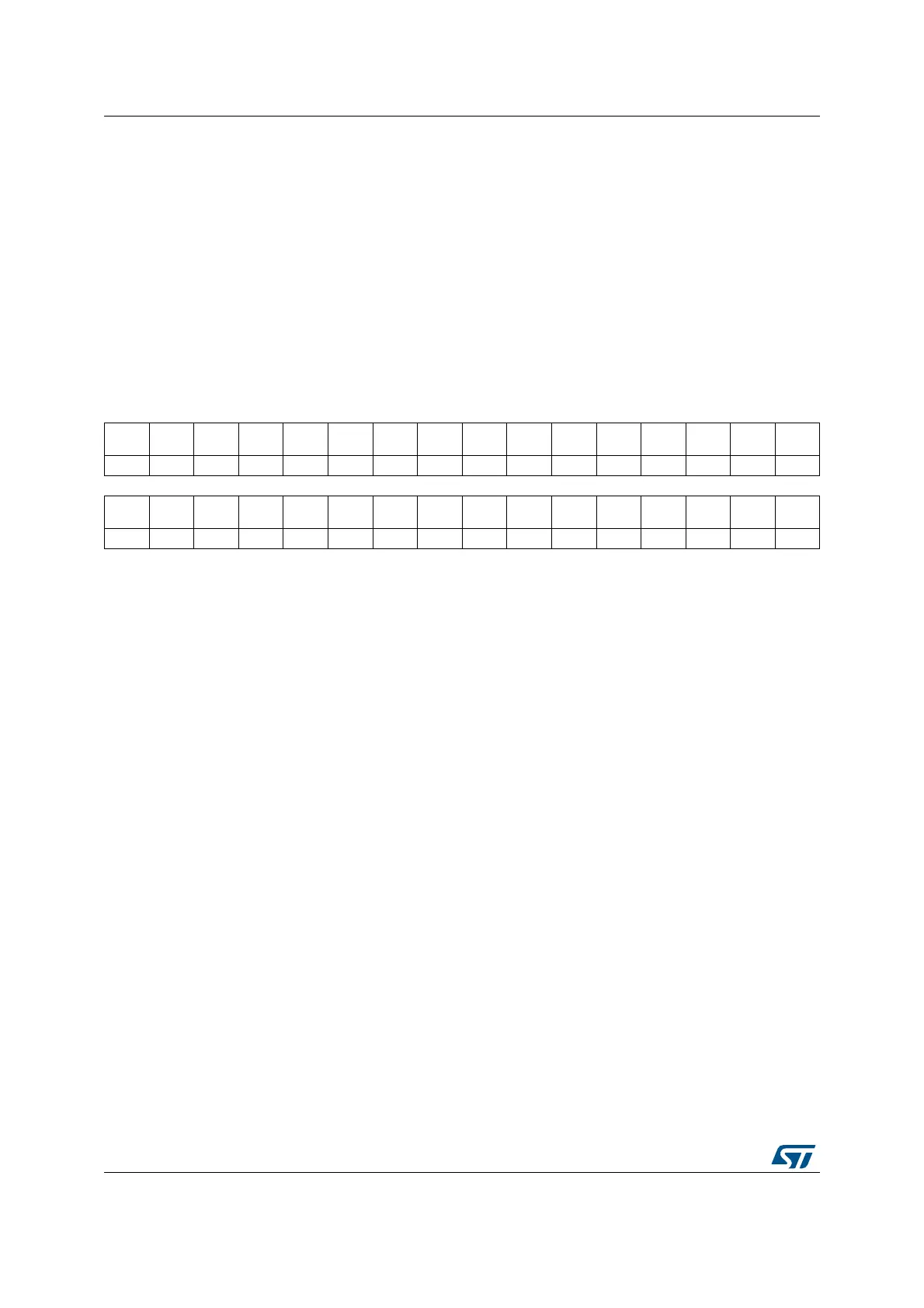

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16

Res. Res. Res. Res. Res. Res. Res. Res. Res.

TIMx

EEFR3

TIMx

CR2

TIMxFL

TR

TIMxO

UTR

TIMxC

HPR

TIMxR

STR

TIMxE

EFR2

rw rw rw rw rw rw rw

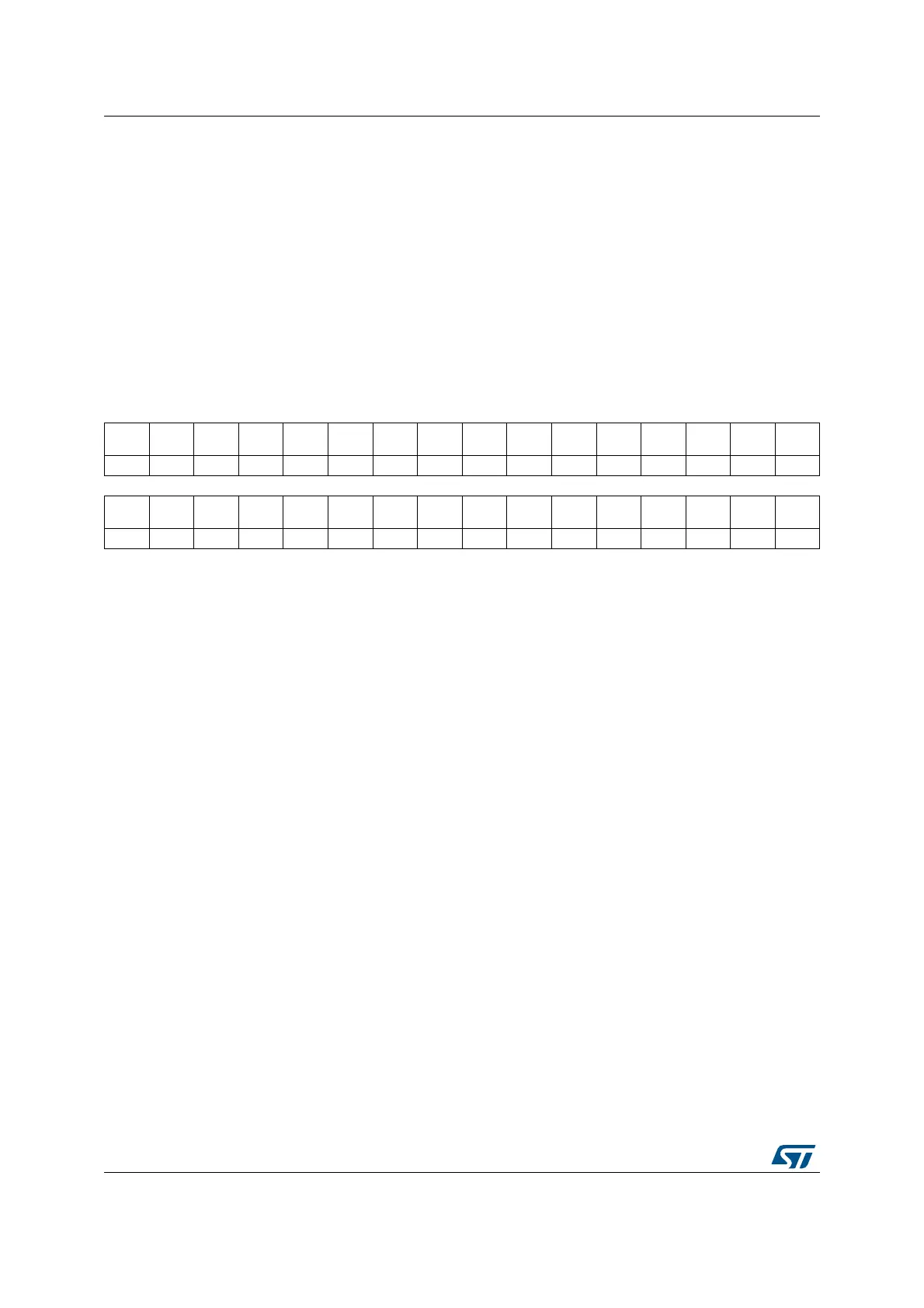

1514131211109876543210

TIMxE

EFR1

TIMxR

ST2R

TIMxS

ET2R

TIMxR

ST1R

TIMxS

ET1R

TIMxD

TxR

TIMxC

MP4

TIMxC

MP3

TIMxC

MP2

TIMxC

MP1

TIMxR

EP

TIMxP

ER

TIMxC

NT

TIMxDI

ER

TIMxIC

R

TIMxC

R

rw rw rw rw rw rw rw rw rw rw rw rw rw rw rw rw

Bits 31:23 Reserved, must be kept at reset value.

Bit 22 TIMxEEFR3: HRTIM_EEFxR3 register update enable

Refer to TIMxCR description.

Bit 21 TIMxCR2: HRTIM_TIMxCR2 register update enable

Refer to TIMxCR description.

Bit 20 TIMxFLTR: HRTIM_FLTxR register update enable

Refer to TIMxCR description.

Bit 19 TIMxOUTR: HRTIM_OUTxR register update enable

Refer to TIMxCR description.

Bit 18 TIMxCHPR: HRTIM_CHPxR register update enable

Refer to TIMxCR description.

Bit 17 TIMxRSTR: HRTIM_RSTxR register update enable

Refer to TIMxCR description.

Bit 16 TIMxEEFR2: HRTIM_EEFxR2 register update enable

Refer to TIMxCR description.

Bit 15 TIMxEEFR1: HRTIM_EEFxR1 register update enable

Refer to TIMxCR description.

Bit 14 TIMxRST2R: HRTIM_RST2xR register update enable

Refer to TIMxCR description.

Bit 13 TIMxSET2R: HRTIM_SET2xR register update enable

Refer to TIMxCR description.

Bit 12 TIMxRST1R: HRTIM_RST1xR register update enable

Refer to TIMxCR description.

Loading...

Loading...