RM0440 Rev 4 1063/2126

RM0440 High-resolution timer (HRTIM)

1083

27.5.75 HRTIM burst DMA data register (HRTIM_BDMADR)

Address offset: 0x3F0

Reset value: 0x0000 0000

Bit 11 TIMxSET1R: HRTIM_SET1xR register update enable

Refer to TIMxCR description.

Bit 10 TIMxDTR: HRTIM_DTxR register update enable

Refer to TIMxCR description.

Bit 9 TIMxCMP4: HRTIM_CMP4xR register update enable

Refer to TIMxCR description.

Bit 8 TIMxCMP3: HRTIM_CMP3xR register update enable

Refer to TIMxCR description.

Bit 7 TIMxCMP2: HRTIM_CMP2xR register update enable

Refer to TIMxCR description.

Bit 6 TIMxCMP1: HRTIM_CMP1xR register update enable

Refer to TIMxCR description.

Bit 5 TIMxREP: HRTIM_REPxR register update enable

Refer to TIMxCR description.

Bit 4 TIMxPER: HRTIM_PERxR register update enable

Refer to TIMxCR description.

Bit 3 TIMxCNT: HRTIM_CNTxR register update enable

Refer to TIMxCR description.

Bit 2 TIMxDIER: HRTIM_TIMxDIER register update enable

Refer to TIMxCR description.

Bit 1 TIMxICR: HRTIM_TIMxICR register update enable

Refer to TIMxCR description.

Bit 0 TIMxCR: HRTIM_TIMxCR register update enable

This bit defines if the master timer MCR register is part of the list of registers to be updated by the

burst DMA.

0: HRTIM_TIMxCR register is not updated by burst DMA accesses

1: HRTIM_TIMxCR register is updated by burst DMA accesses

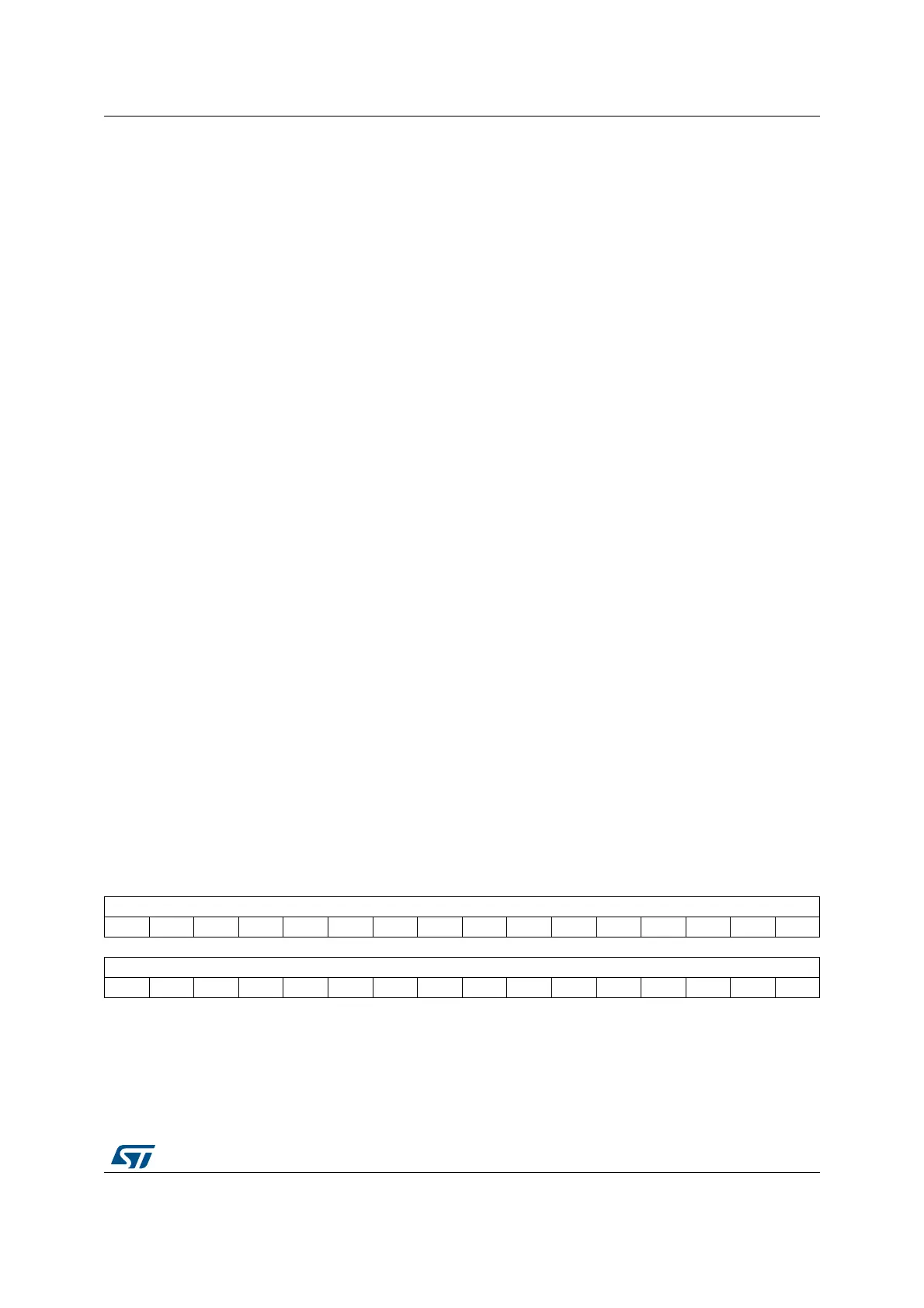

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16

BDMADR[31:16]

wo wo wo wo wo wo wo wo wo wo wo wo wo wo wo wo

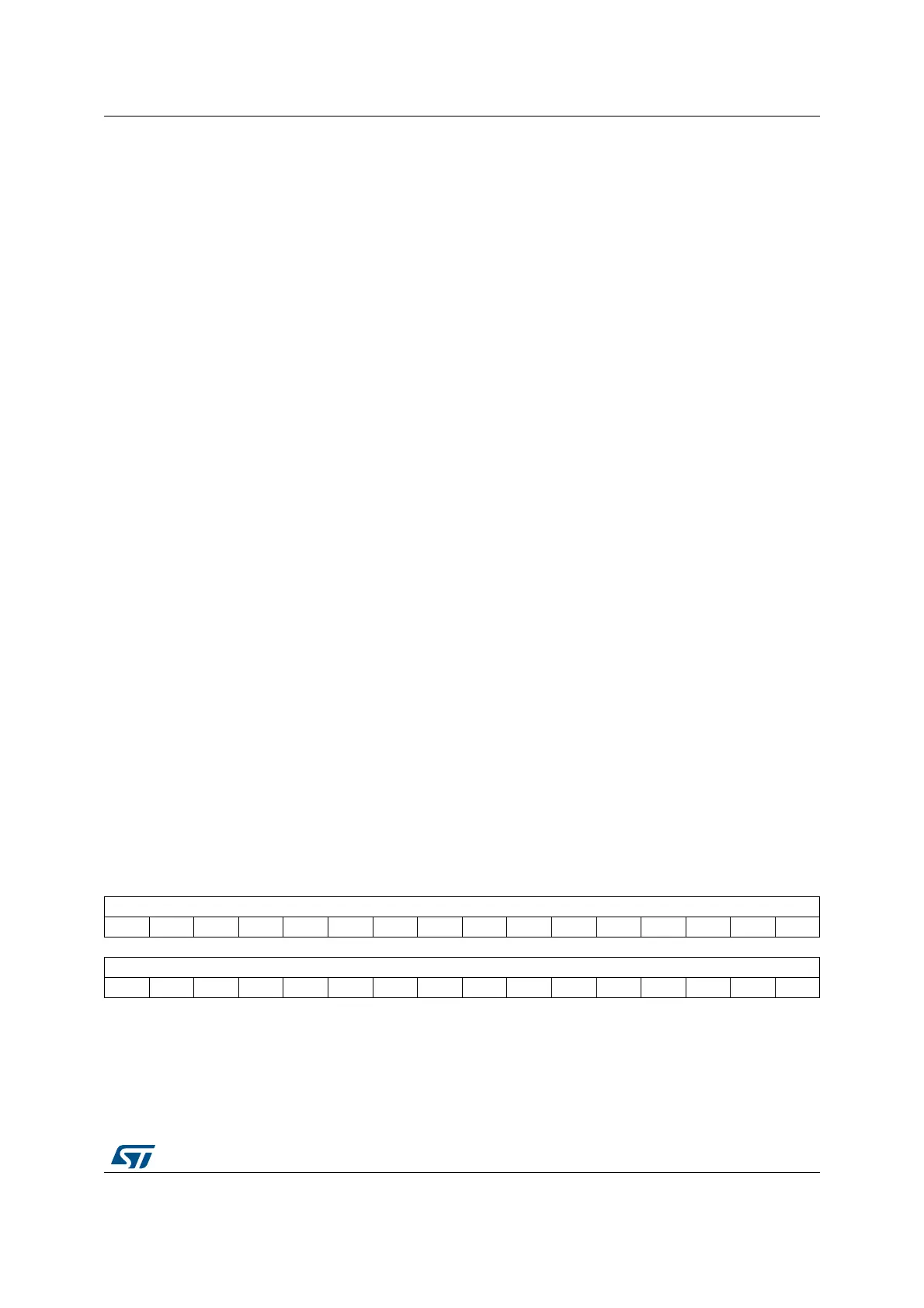

1514131211109876543210

BDMADR[15:0]

wo wo wo wo wo wo wo wo wo wo wo wo wo wo wo wo

Bits 31:0 BDMADR[31:0]: Burst DMA data register

Write accesses to this register triggers:

– the copy of the data value into the registers enabled in BDTxUPR and BDMUPR register

bits

– the increment of the register pointer to the next location to be filled

Loading...

Loading...