RM0440 Rev 4 1185/2126

RM0440 Advanced-control timers (TIM1/TIM8/TIM20)

1226

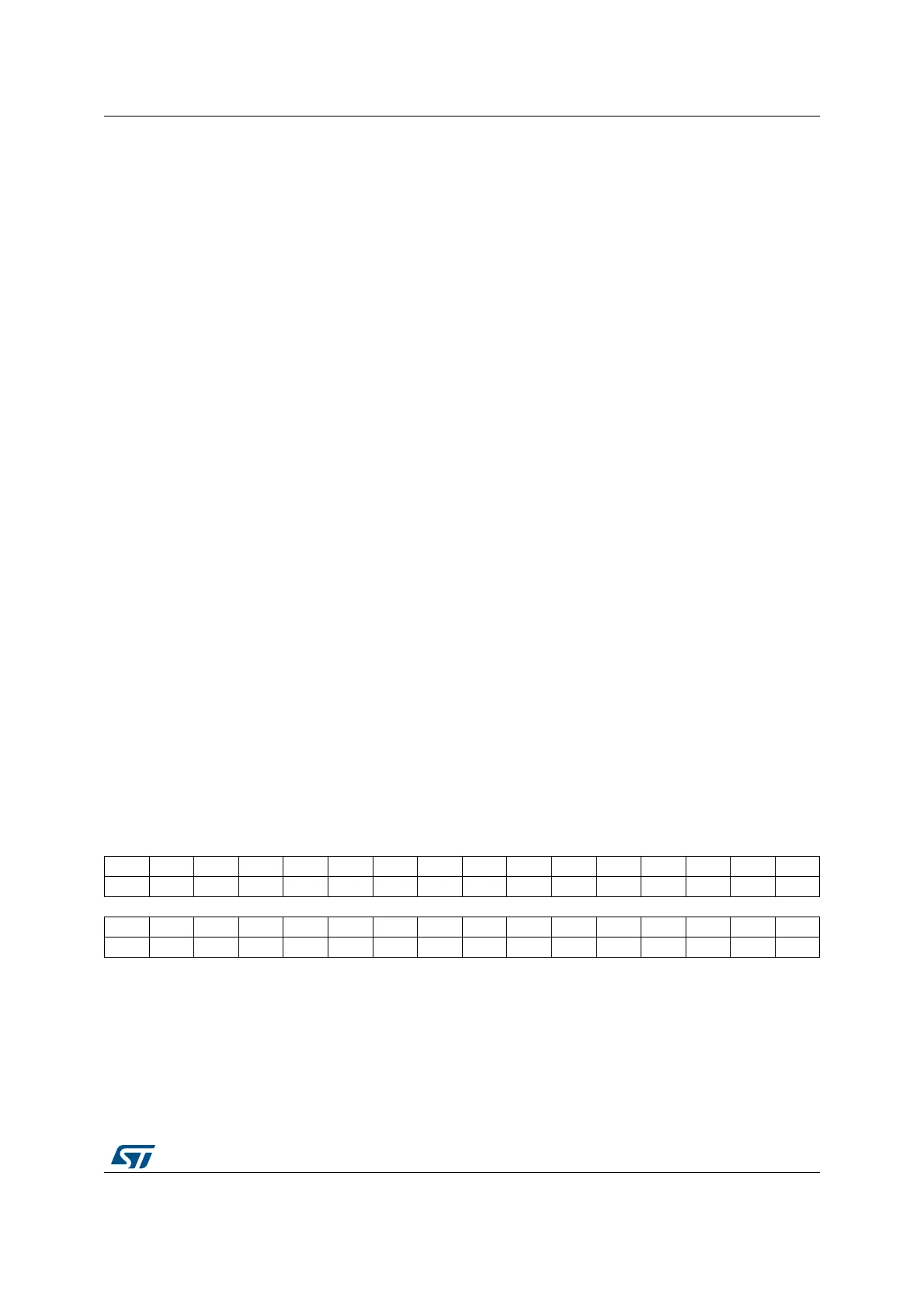

28.6.5 TIMx status register (TIMx_SR)(x = 1, 8, 20)

Address offset: 0x010

Reset value: 0x0000 0000

Bit 8 UDE: Update DMA request enable

0: Update DMA request disabled

1: Update DMA request enabled

Bit 7 BIE: Break interrupt enable

0: Break interrupt disabled

1: Break interrupt enabled

Bit 6 TIE: Trigger interrupt enable

0: Trigger interrupt disabled

1: Trigger interrupt enabled

Bit 5 COMIE: COM interrupt enable

0: COM interrupt disabled

1: COM interrupt enabled

Bit 4 CC4IE: Capture/compare 4 interrupt enable

0: CC4 interrupt disabled

1: CC4 interrupt enabled

Bit 3 CC3IE: Capture/compare 3 interrupt enable

0: CC3 interrupt disabled

1: CC3 interrupt enabled

Bit 2 CC2IE: Capture/compare 2 interrupt enable

0: CC2 interrupt disabled

1: CC2 interrupt enabled

Bit 1 CC1IE: Capture/compare 1 interrupt enable

0: CC1 interrupt disabled

1: CC1 interrupt enabled

Bit 0 UIE: Update interrupt enable

0: Update interrupt disabled

1: Update interrupt enabled

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16

Res. Res. Res. Res. Res. Res. Res. Res. TERRF IERRF DIRF IDXF Res. Res. CC6IF CC5IF

rc_w0 rc_w0 rc_w0 rc_w0 rc_w0 rc_w0

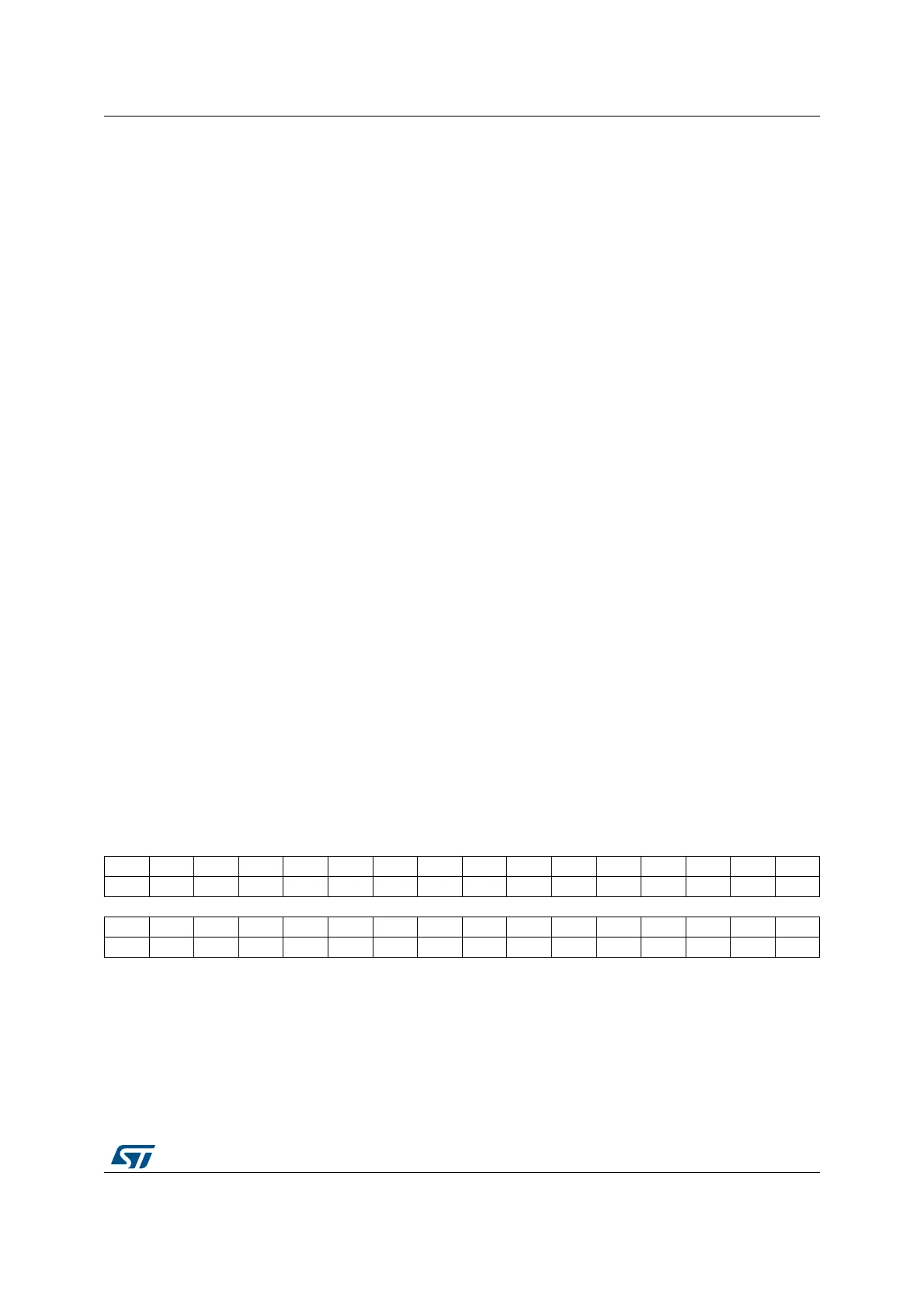

1514131211109876543210

Res. Res. SBIF CC4OF CC3OF CC2OF CC1OF B2IF BIF TIF COMIF CC4IF CC3IF CC2IF CC1IF UIF

rc_w0 rc_w0 rc_w0 rc_w0 rc_w0 rc_w0 rc_w0 rc_w0 rc_w0 rc_w0 rc_w0 rc_w0 rc_w0 rc_w0

Loading...

Loading...