Advanced-control timers (TIM1/TIM8/TIM20) RM0440

1214/2126 RM0440 Rev 4

28.6.24 TIMx timer deadtime register 2 (TIMx_DTR2)(x = 1, 8, 20)

Address offset: 0x054

Reset value: 0x0000 0000

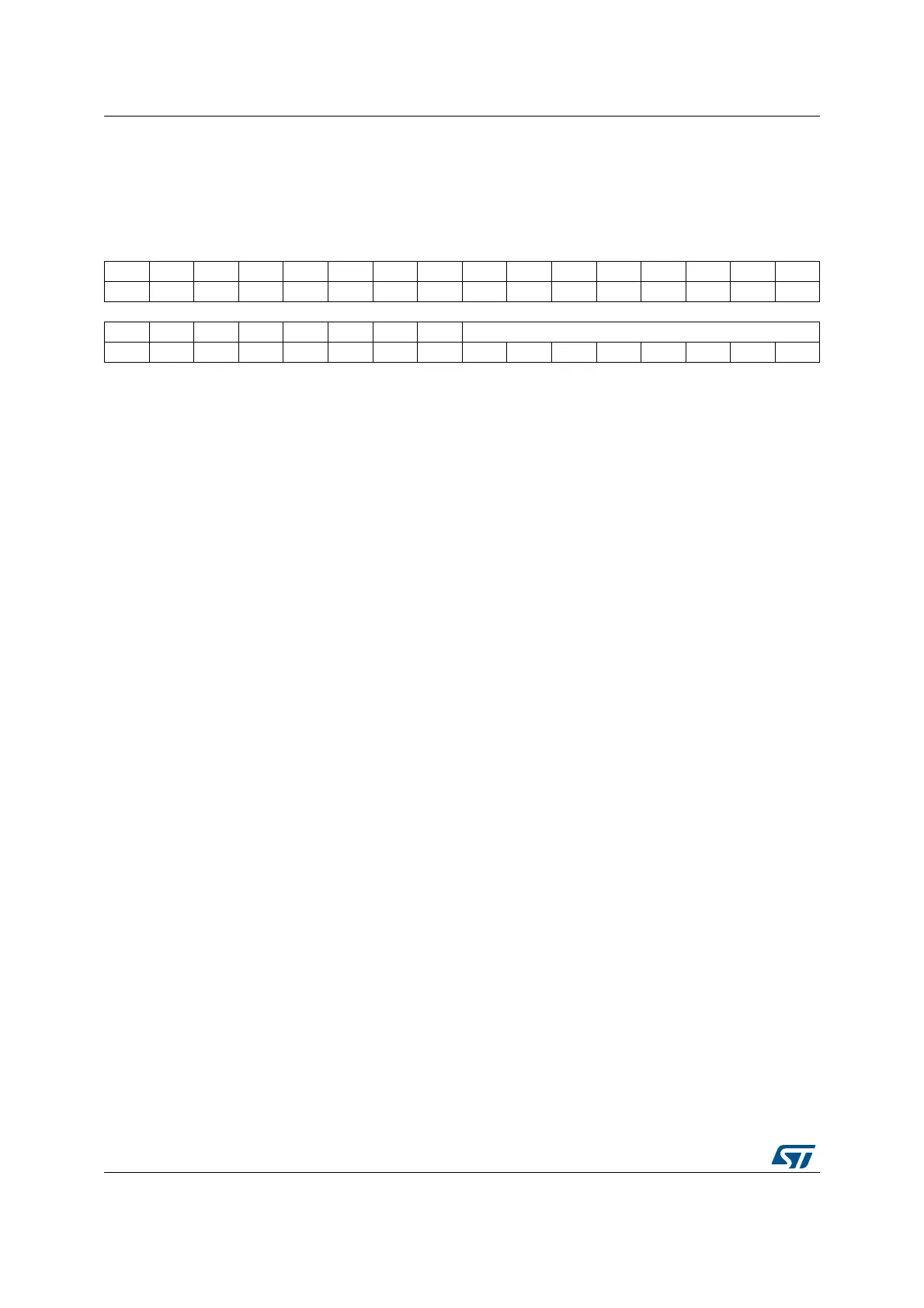

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16

Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. DTPE DTAE

rw rw

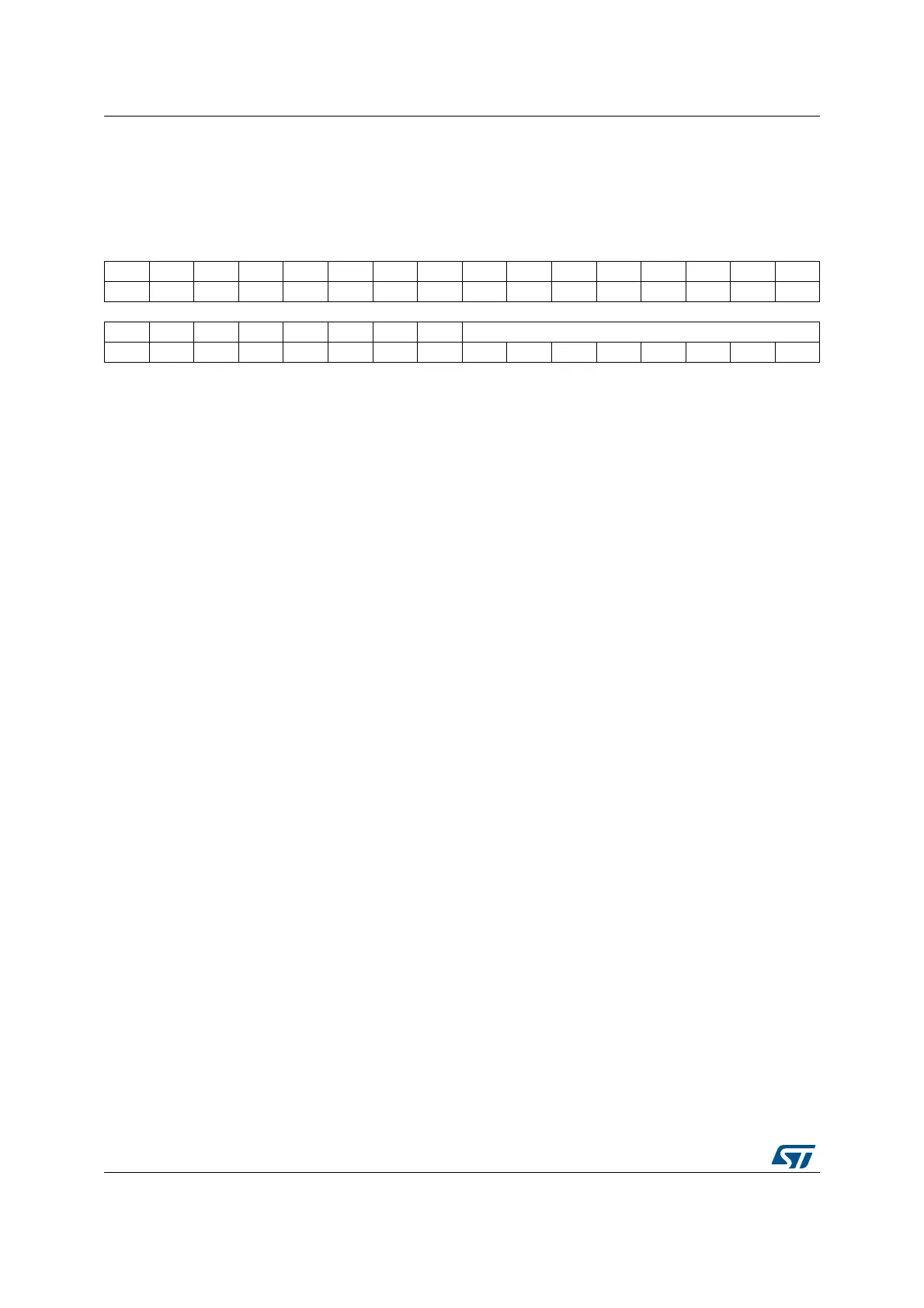

1514131211109876543210

Res. Res. Res. Res. Res. Res. Res. Res. DTGF[7:0]

rw rw rw rw rw rw rw rw

Bits 31:18 Reserved, must be kept at reset value.

Bit 17 DTPE: Deadtime preload enable

0: Deadtime value is not preloaded

1: Deadtime value preload is enabled

Note: This bit can not be modified as long as LOCK level 1, 2 or 3 has been programmed

(LOCK bits in TIMx_BDTR register).

Bit 16 DTAE: Deadtime asymmetric enable

0: Deadtime on rising and falling edges are identical, and defined with DTG[7:0] register

1: Deadtime on rising edge is defined with DTG[7:0] register and deadtime on falling edge is

defined with DTGF[7:0] bits.

Note: This bit can not be modified as long as LOCK level 1, 2 or 3 has been programmed

(LOCK bits in TIMx_BDTR register).

Bits 15:8 Reserved, must be kept at reset value.

Bits 7:0 DTGF[7:0]: Dead-time falling edge generator setup

This bit-field defines the duration of the dead-time inserted between the complementary

outputs, on the falling edge.

DTGF[7:5]=0xx => DTF=DTGF[7:0]x t

dtg

with t

dtg

=t

DTS

.

DTGF[7:5]=10x => DTF=(64+DTGF[5:0])xt

dtg

with T

dtg

=2xt

DTS

.

DTGF[7:5]=110 => DTF=(32+DTGF[4:0])xt

dtg

with T

dtg

=8xt

DTS

.

DTGF[7:5]=111 => DTF=(32+DTGF[4:0])xt

dtg

with T

dtg

=16xt

DTS

.

Example if T

DTS

=125ns (8MHz), dead-time possible values are:

0 to 15875 ns by 125 ns steps,

16 us to 31750 ns by 250 ns steps,

32 us to 63us by 1 us steps,

64 us to 126 us by 2 us steps

Note: This bit-field can not be modified as long as LOCK level 1, 2 or 3 has been programmed

(LOCK bits in TIMx_BDTR register).

Loading...

Loading...