RM0440 Rev 4 1215/2126

RM0440 Advanced-control timers (TIM1/TIM8/TIM20)

1226

28.6.25 TIMx timer encoder control register (TIMx_ECR)(x = 1, 8, 20)

Address offset: 0x058

Reset value: 0x0000 0000

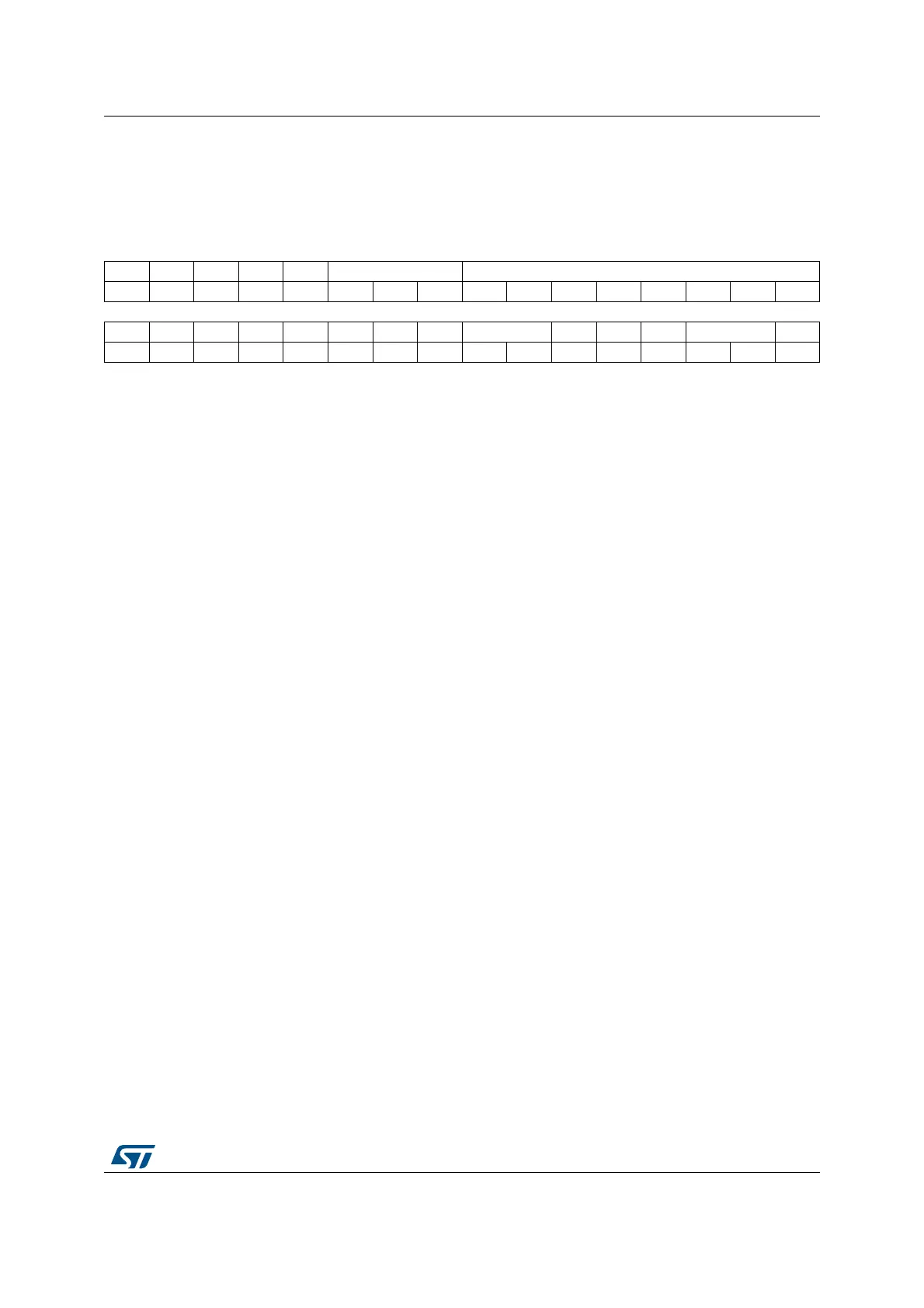

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16

Res. Res. Res. Res. Res. PWPRSC[2:0] PW[7:0]

rw rw rw rw rw rw rw rw rw rw rw

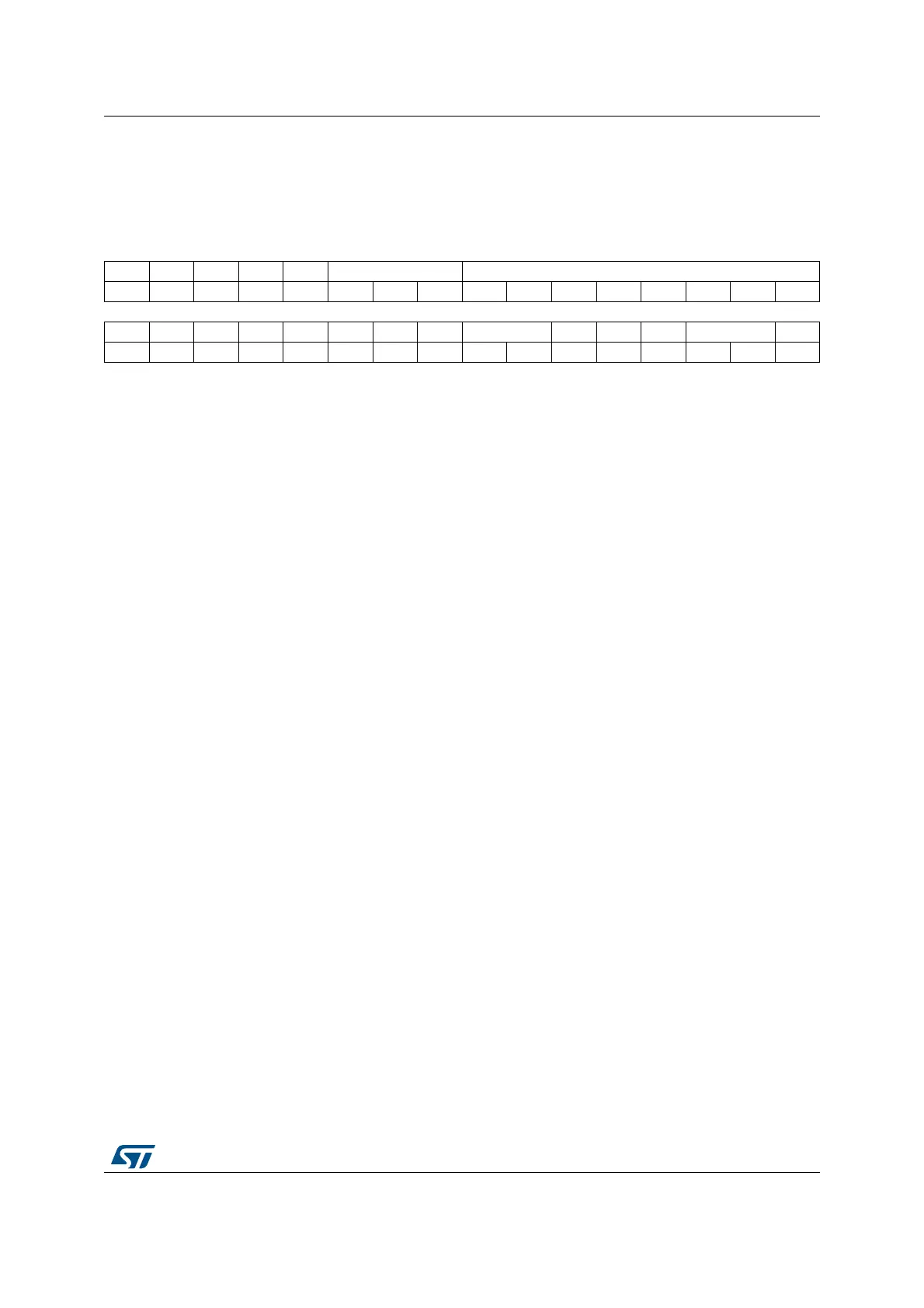

1514131211109876543210

Res. Res. Res. Res. Res. Res. Res. Res. IPOS[1:0] FIDX Res. Res. IDIR[1:0] IE

rw rw rw rw rw rw

Bits 31:27 Reserved, must be kept at reset value.

Bits 26:24 PWPRSC[2:0]: Pulse width prescaler

This bitfield sets the clock prescaler for the pulse generator, as following:

t

PWG

= (2

(PWPRSC[2:0])

) x t

tim_ker_ck

Bits 23:16 PW[7:0]: Pulse width

This bitfield defines the pulse duration, as following:

t

PW

= PW[7:0] x t

PWG

Bits 15:8 Reserved, must be kept at reset value.

Bits 7:6 IPOS[1:0]: Index positioning

In quadrature encoder mode (SMS[3:0] = 0001, 0010, 0011, 1110, 1111), this bit indicates in

which AB input configuration the Index event resets the counter.

00: Index resets the counter when AB = 00

01: Index resets the counter when AB = 01

10: Index resets the counter when AB = 10

11: Index resets the counter when AB = 11

In directional clock mode or clock plus direction mode (SMS[3:0] = 1010, 1011, 1100, 1101),

these bits indicates on which level the Index event resets the counter. In bidirectional clock

mode, this applies for both clock inputs.

x0: Index resets the counter when clock is 0

x1: Index resets the counter when clock is 1

Note: IPOS[1] bit is not significant

Bit 5 FIDX: First index

This bit indicates if the first index only is taken into account

0: Index is always active

1: the first Index only resets the counter

Loading...

Loading...