Low-power universal asynchronous receiver transmitter (LPUART) RM0440

1712/2126 RM0440 Rev 4

38.6.2 LPUART control register 1 [alternate] (LPUART_CR1)

Address offset: 0x00

Reset value: 0x0000 0000

The same register can be used in FIFO mode enabled (previous section) and FIFO mode

disabled (this section).

FIFO mode disabled

Bit 2 RE: Receiver enable

This bit enables the receiver. It is set and cleared by software.

0: Receiver is disabled

1: Receiver is enabled and begins searching for a start bit

Bit 1 UESM: LPUART enable in Stop mode

When this bit is cleared, the LPUART is not able to wake up the MCU from low-power mode.

When this bit is set, the LPUART is able to wake up the MCU from low-power mode,

provided that the LPUART clock selection is HSI16 or LSE in the RCC.

This bit is set and cleared by software.

0: LPUART not able to wake up the MCU from low-power mode.

1: LPUART able to wake up the MCU from low-power mode. When this function is active,

the clock source for the LPUART must be HSI16 or LSE (see RCC chapter)

Note: It is recommended to set the UESM bit just before entering low-power mode and clear

it on exit from low-power mode.

Bit 0 UE: LPUART enable

When this bit is cleared, the LPUART prescalers and outputs are stopped immediately, and

current operations are discarded. The configuration of the LPUART is kept, but all the status

flags, in the LPUART_ISR are reset. This bit is set and cleared by software.

0: LPUART prescaler and outputs disabled, low-power mode

1: LPUART enabled

Note: To enter low-power mode without generating errors on the line, the TE bit must be reset

before and the software must wait for the TC bit in the LPUART_ISR to be set before

resetting the UE bit.

The DMA requests are also reset when UE = 0 so the DMA channel must be disabled

before resetting the UE bit.

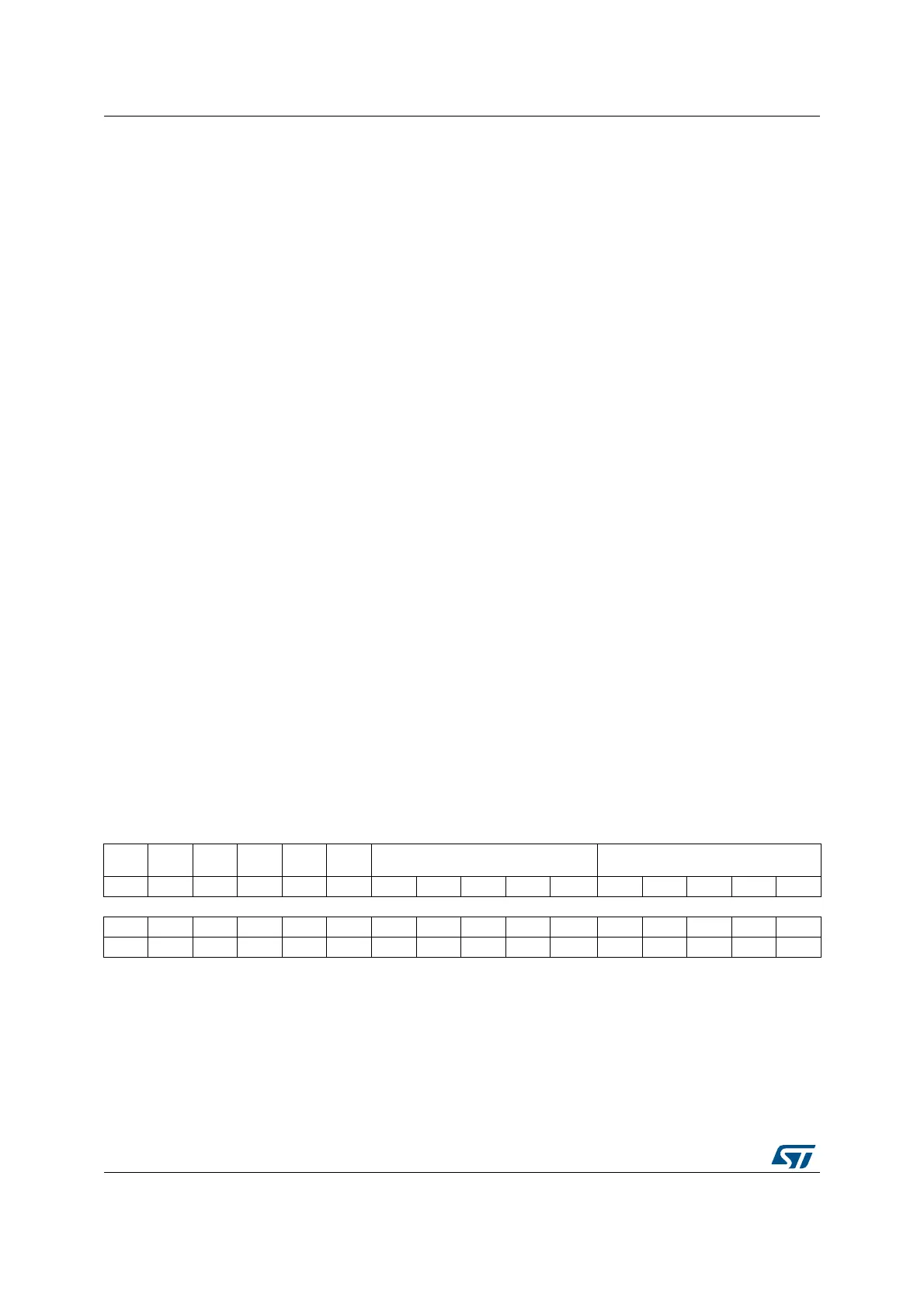

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16

Res. Res.

FIFO

EN

M1 Res. Res. DEAT[4:0] DEDT[4:0]

rw rw rw rw rw rw rw rw rw rw rw rw

15141312111098765 43210

Res. CMIE MME M0 WAKE PCE PS PEIE TXEIE TCIE RXNEIE IDLEIE TE RE UESM UE

rw rw rw rw rw rw rw rw rw rw rw rw rw rw rw

Loading...

Loading...