RM0440 Rev 4 713/2126

RM0440 Analog-to-digital converters (ADC)

724

21.6.19 ADC analog watchdog 2 configuration register (ADC_AWD2CR)

Address offset: 0xA0

Reset value: 0x0000 0000

21.6.20 ADC analog watchdog 3 configuration register (ADC_AWD3CR)

Address offset: 0xA4

Reset value: 0x0000 0000

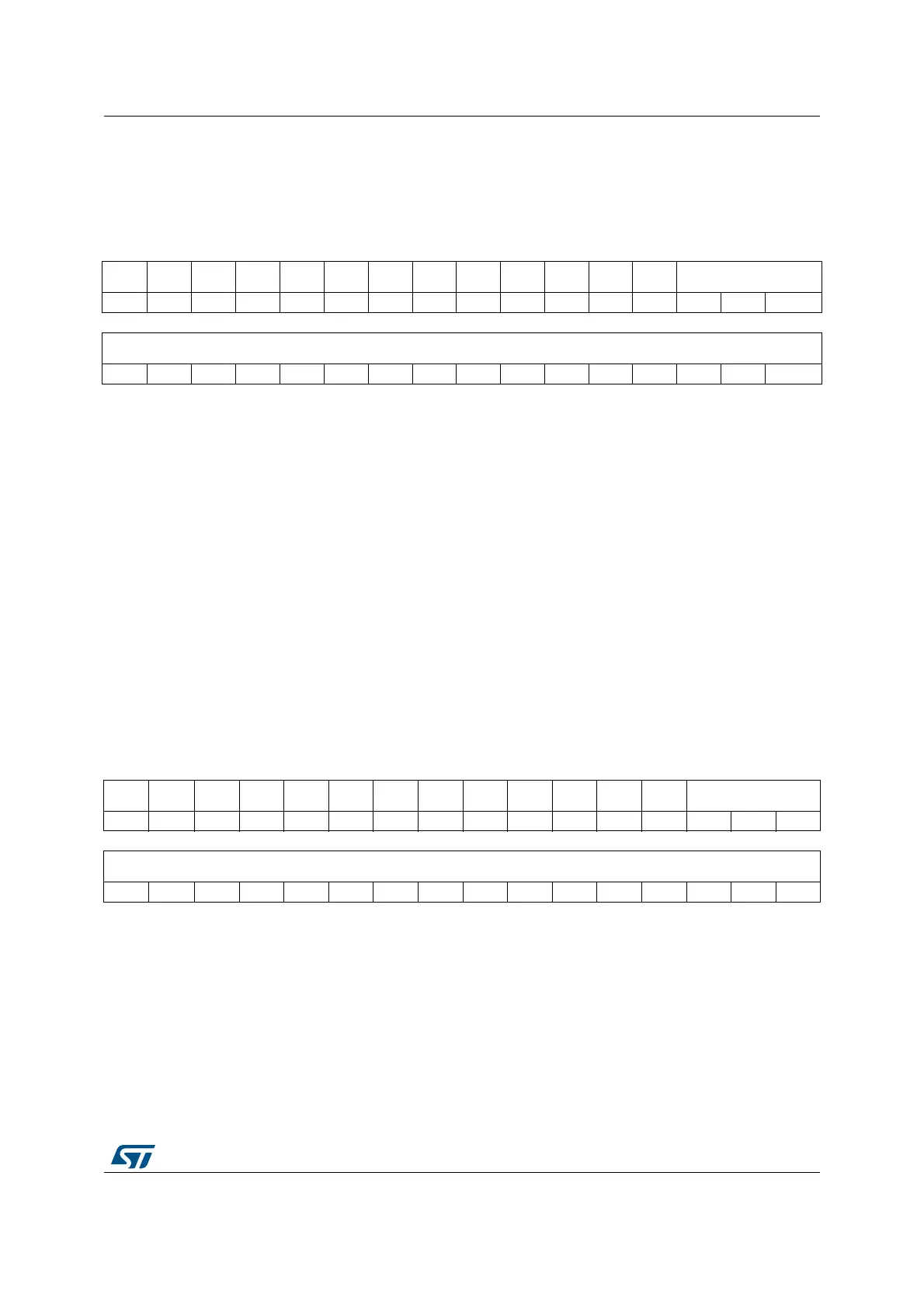

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16

Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. AWD2CH[18:16]

rw rw rw

151413121110987654321 0

AWD2CH[15:0]

rw rw rw rw rw rw rw rw rw rw rw rw rw rw rw rw

Bits 31:19 Reserved, must be kept at reset value.

Bits 18:0 AWD2CH[18:0]: Analog watchdog 2 channel selection

These bits are set and cleared by software. They enable and select the input channels to be guarded

by the analog watchdog 2.

AWD2CH[i] = 0: ADC analog input channel i is not monitored by AWD2

AWD2CH[i] = 1: ADC analog input channel i is monitored by AWD2

When AWD2CH[18:0] = 000..0, the analog watchdog 2 is disabled

Note: The channels selected by AWD2CH must be also selected into the SQRi or JSQRi registers.

The software is allowed to write these bits only when ADSTART=0 and JADSTART=0 (which

ensures that no conversion is ongoing).

Some channels are not connected physically and must not be selected for the analog

watchdog.

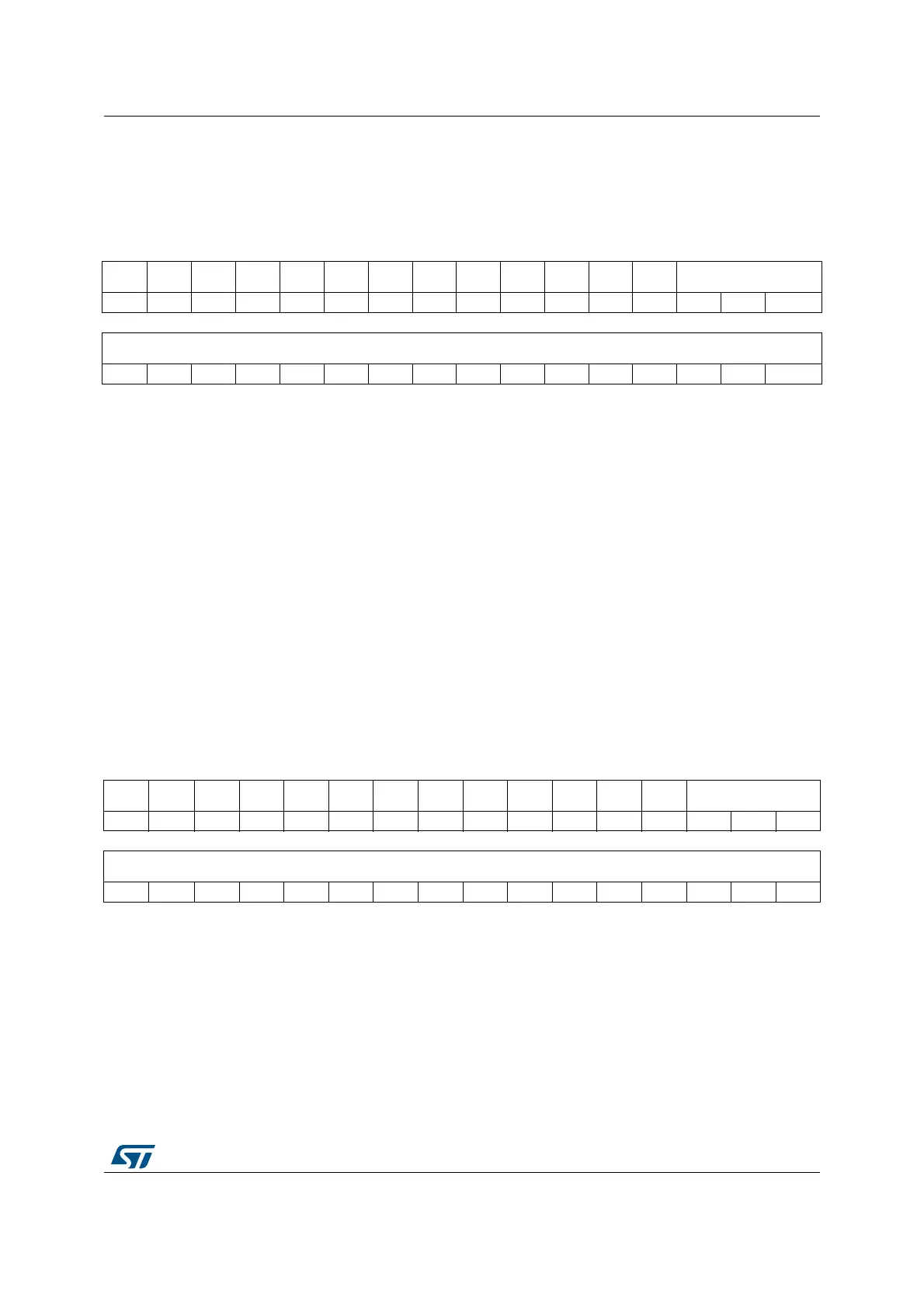

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16

Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. AWD3CH[18:16]

rw rw rw

1514131211109876543210

AWD3CH[15:0]

rw rw rw rw rw rw rw rw rw rw rw rw rw rw rw rw

Loading...

Loading...