RM0440 Rev 4 967/2126

RM0440 High-resolution timer (HRTIM)

1083

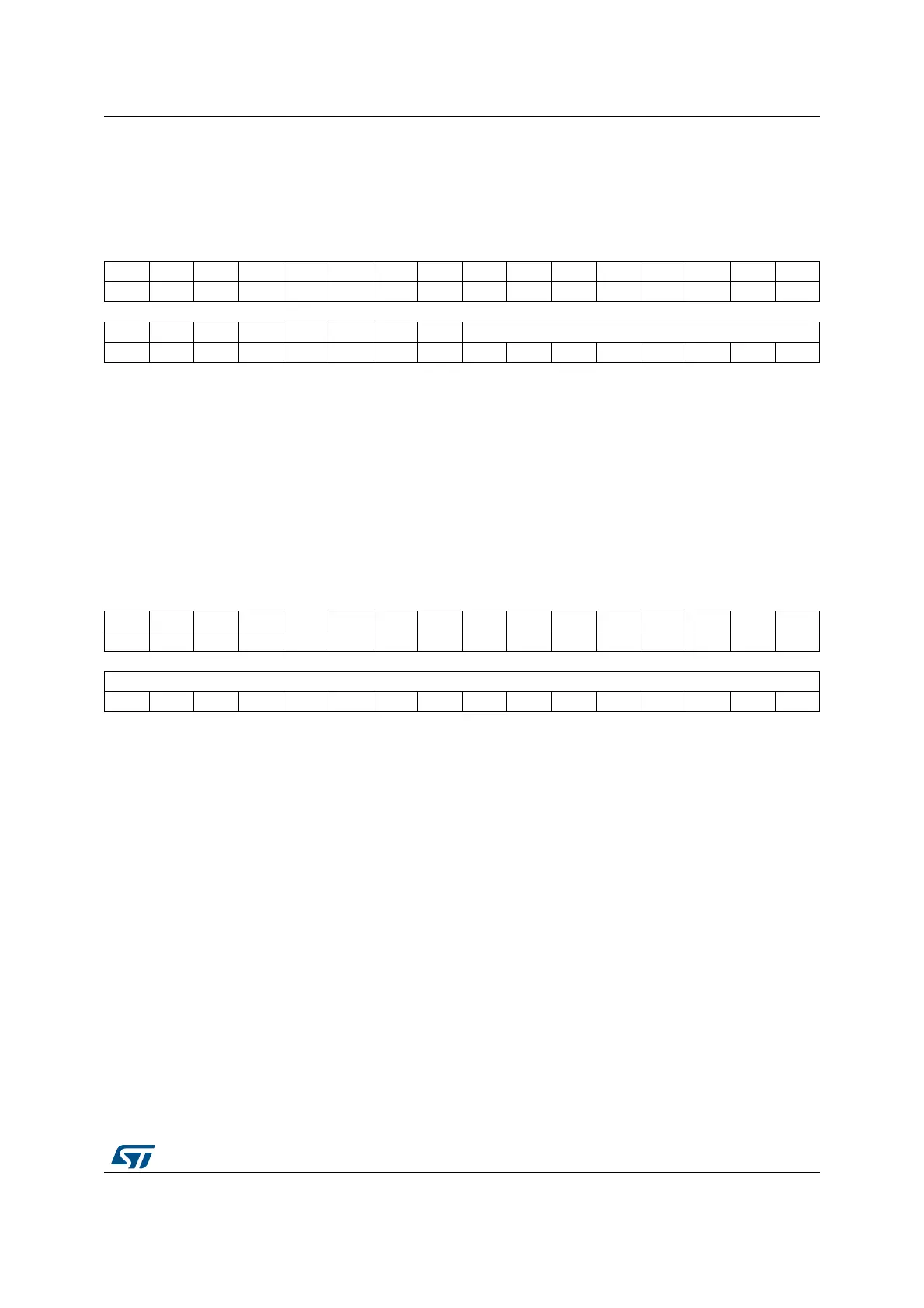

27.5.7 HRTIM master timer repetition register (HRTIM_MREP)

Address offset: 0x018

Reset value: 0x0000 0000

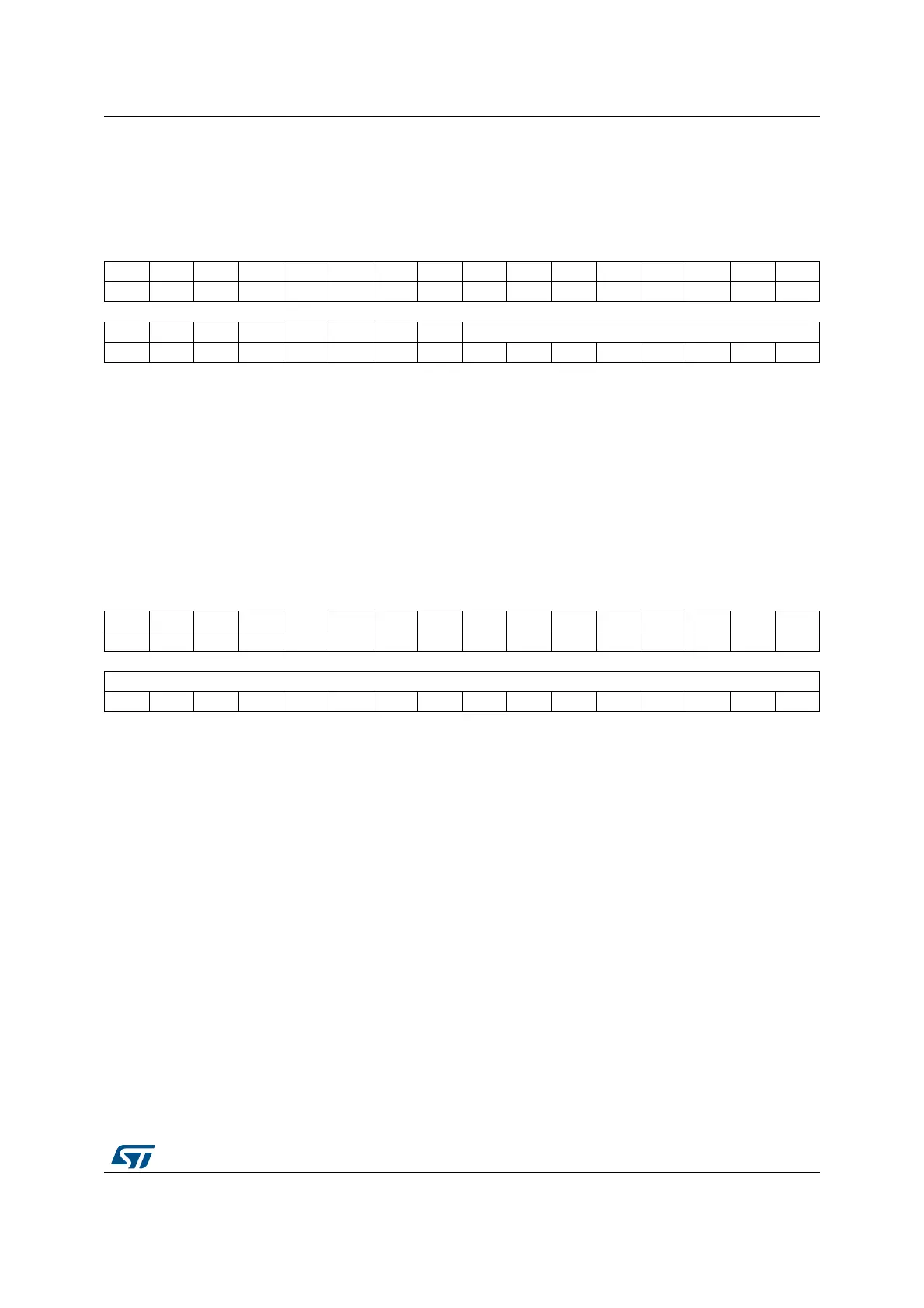

27.5.8 HRTIM master timer compare 1 register (HRTIM_MCMP1R)

Address offset: 0x01C

Reset value: 0x0000 0000

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16

Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res.

1514131211109876543210

Res. Res. Res. Res. Res. Res. Res. Res. MREP[7:0]

rw rw rw rw rw rw rw rw

Bits 31:8 Reserved, must be kept at reset value.

Bits 7:0 MREP[7:0]: Master timer repetition period value

This register holds the repetition period value for the master counter. It is either the preload register

or the active register if preload is disabled.

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16

Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res.

1514131211109876543210

MCMP1[15:0]

rw rw rw rw rw rw rw rw rw rw rw rw rw rw rw rw

Bits 31:16 Reserved, must be kept at reset value.

Bits 15:0 MCMP1[15:0]: Master timer compare 1 value

This register holds the master timer compare 1 value. It is either the preload register or the active

register if preload is disabled.

The compare value must be above or equal to 3 periods of the f

H

RTIM

clock, that is 0x60 if

CKPSC[2:0] = 0, 0x30 if CKPSC[2:0] = 1, 0x18 if CKPSC[2:0] = 2,...

Loading...

Loading...