RM0440 Rev 4 309/2126

RM0440 Reset and clock control (RCC)

338

7.4.15 AHB2 peripheral clock enable register (RCC_AHB2ENR)

Address offset: 0x4C

Reset value: 0x0000 0000

Access: no wait state, word, half-word and byte access

Note: When the peripheral clock is not active, the peripheral registers read or write access is not

supported.

Bit 2 DMAMUX1EN: DMAMUX1 clock enable

Set and reset by software.

0: DMAMUX1 clock disabled

1: DMAMUX1 clock enabled

Bit 1 DMA2EN: DMA2 clock enable

Set and cleared by software.

0: DMA2 clock disable

1: DMA2 clock enable

Bit 0 DMA1EN: DMA1 clock enable

Set and cleared by software.

0: DMA1 clock disable

1: DMA1 clock enable

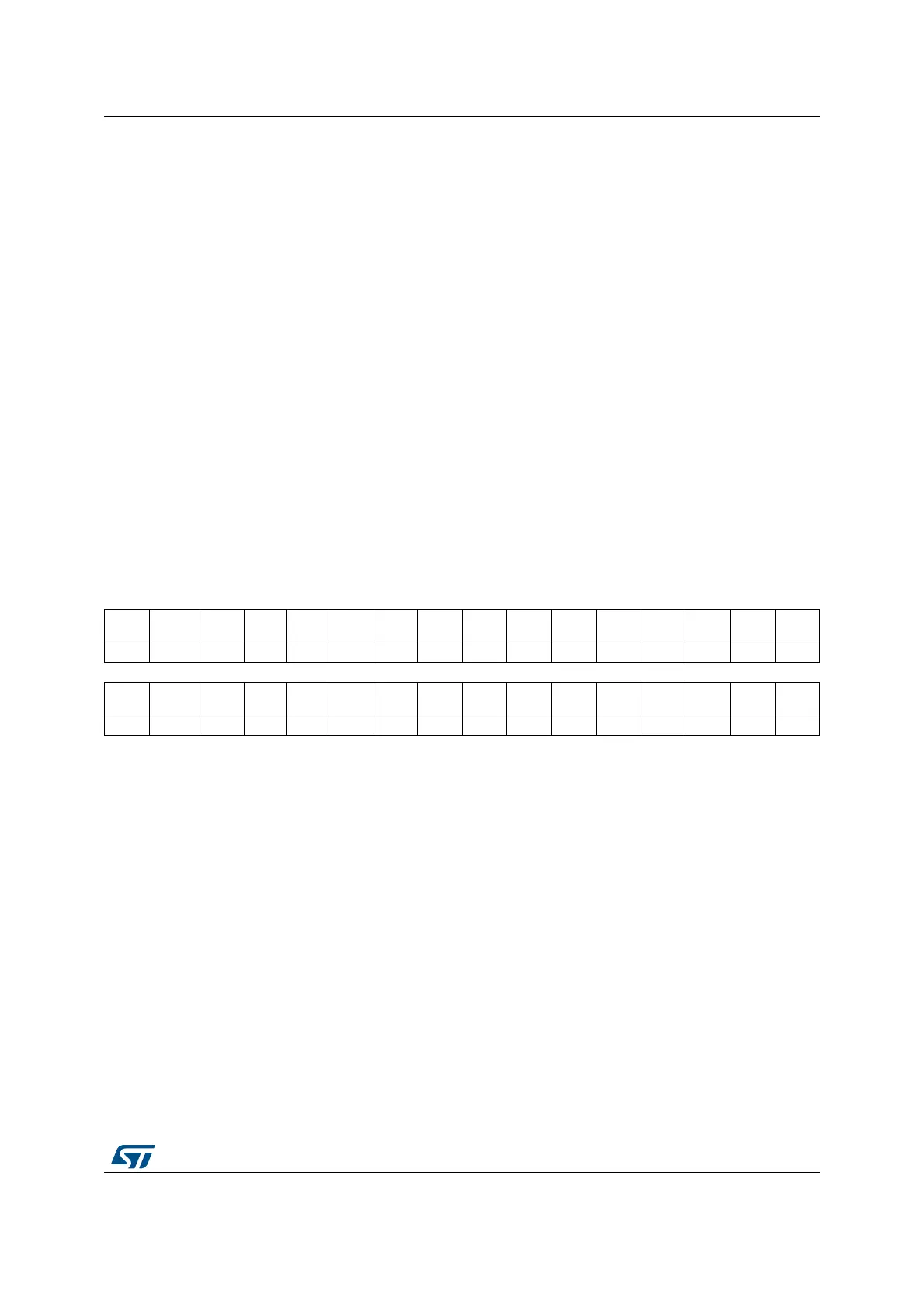

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16

Res. Res. Res. Res. Res.

RNG

EN

Res.

AES

EN

Res. Res. Res. Res.

DAC4

EN

DAC3

EN

DAC2

EN

DAC1

EN

rw rw rw rw rw rw

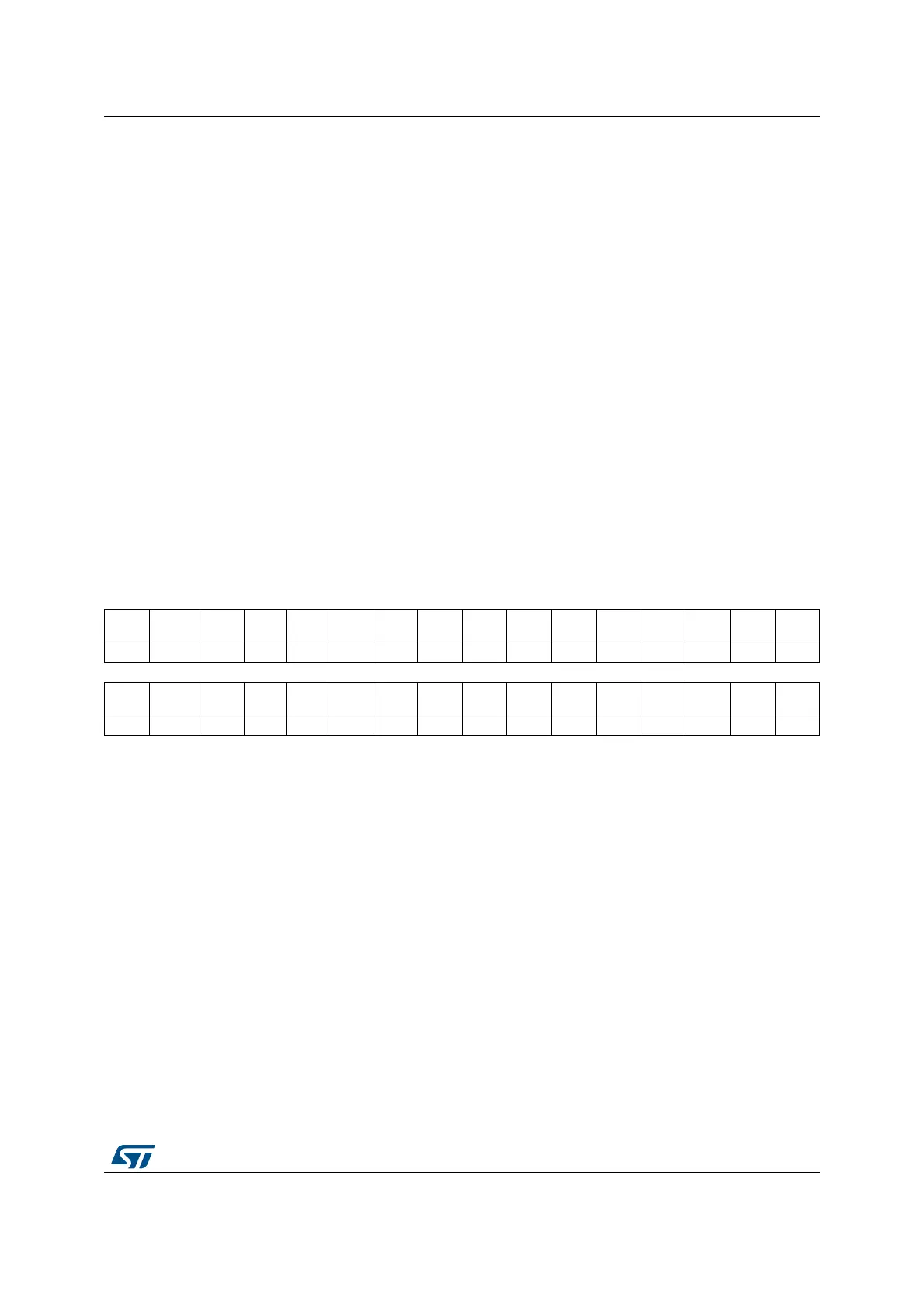

1514131211109876543210

Res.

ADC345

EN

ADC12

EN

Res. Res. Res. Res. Res. Res.

GPIOG

EN

GPIOF

EN

GPIOE

EN

GPIOD

EN

GPIOC

EN

GPIOB

EN

GPIOA

EN

rw rw rw rw rw rw rw rw rw

Bits 31:27 Reserved, must be kept at reset value.

Bit 26 RNGEN: RNG enable

Set and cleared by software.

0: RNG disabled

1: RNG enabled

Bit 25 Reserved, must be kept at reset value.

Bit 24 AESEN: AES clock enable

Set and cleared by software.

0: AES clock disabled

1: AES clock enabled

Bits 23:20 Reserved, must be kept at reset value.

Bit 19 DAC4EN: DAC4 clock enable

Set and cleared by software.

0: DAC4 clock disabled

1: DAC4 clock enabled

Loading...

Loading...