RM0453 Rev 5 127/1450

RM0453 Embedded flash memory (FLASH)

154

When at least one PES bit is set, the following occurs:

• Any ongoing program or erase operation is completed.

The maximum latency for a flash program erase suspension is the maximum time for

one program or erase operation to complete (see product datasheets for more

information on the flash program and erase timing).

• All new requested program and erase operations is not started but suspended.

PESD bits in FLASH_SR and FLASH_C2SR are set as soon as any PES is set, no

matter if a program/erase is currently suspended. This allows a CPU to test PESD prior

to requesting a program or an erase operation.

When all PES bits are reset to 0, a suspended program or erase operation is started: the

PESD bits are cleared.

4.8 FLASH interrupts

4.8.1 Illegal access interrupts

Unprivileged access to privileged registers generates an illegal access event. This event is

connected to the GTZC_TZIC.

Non-secure access to secure registers generates an illegal access event. This event is

connected to the GTZC_TZIC.

For more information on illegal access events see: Section 3: Global security controller

(GTZC).

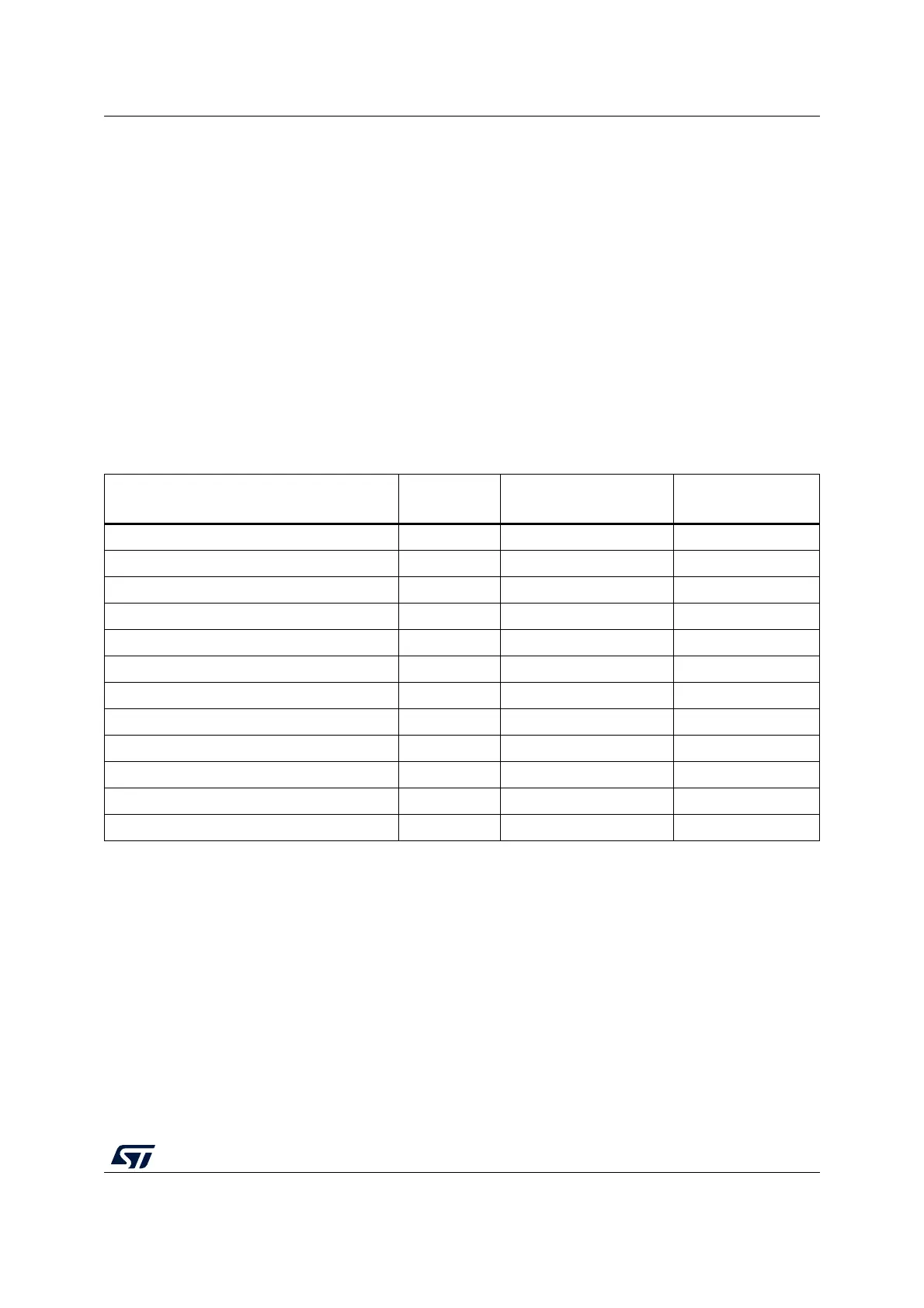

Table 23. Flash interrupt requests

Interrupt event Event flag

Event flag/interrupt

clearing method

Interrupt enable

control bit

End of operation EOP

(1)

Write EOP=1 EOPIE

Operation error OPERR

(2)

Write OPERR=1 ERRIE

Readout protection error RDERR Write RDERR=1 RDERRIE

Write protection error WRPERR Write WRPERR=1 N/A

Size error SIZERR Write SIZERR=1 N/A

Programming sequential error PROGERR Write PROGERR=1 N/A

Programming alignment error PGAERR Write PGAERR=1 N/A

Programming sequence error PGSERR Write PGSERR=1 N/A

Data miss during fast programming error MISSERR Write MISSERR=1 N/A

Fast programming error FASTERR Write FASTERR=1 N/A

ECC error correction ECCC Write ECCC=1 ECCCIE

ECC double-error (NMI) ECCD Write ECCD=1 N/A

1. EOP is set only if EOPIE is set.

2. OPERR is set only if ERRIE is set.

Loading...

Loading...