RM0453 Rev 5 507/1450

RM0453 Extended interrupts and event controller (EXTI)

524

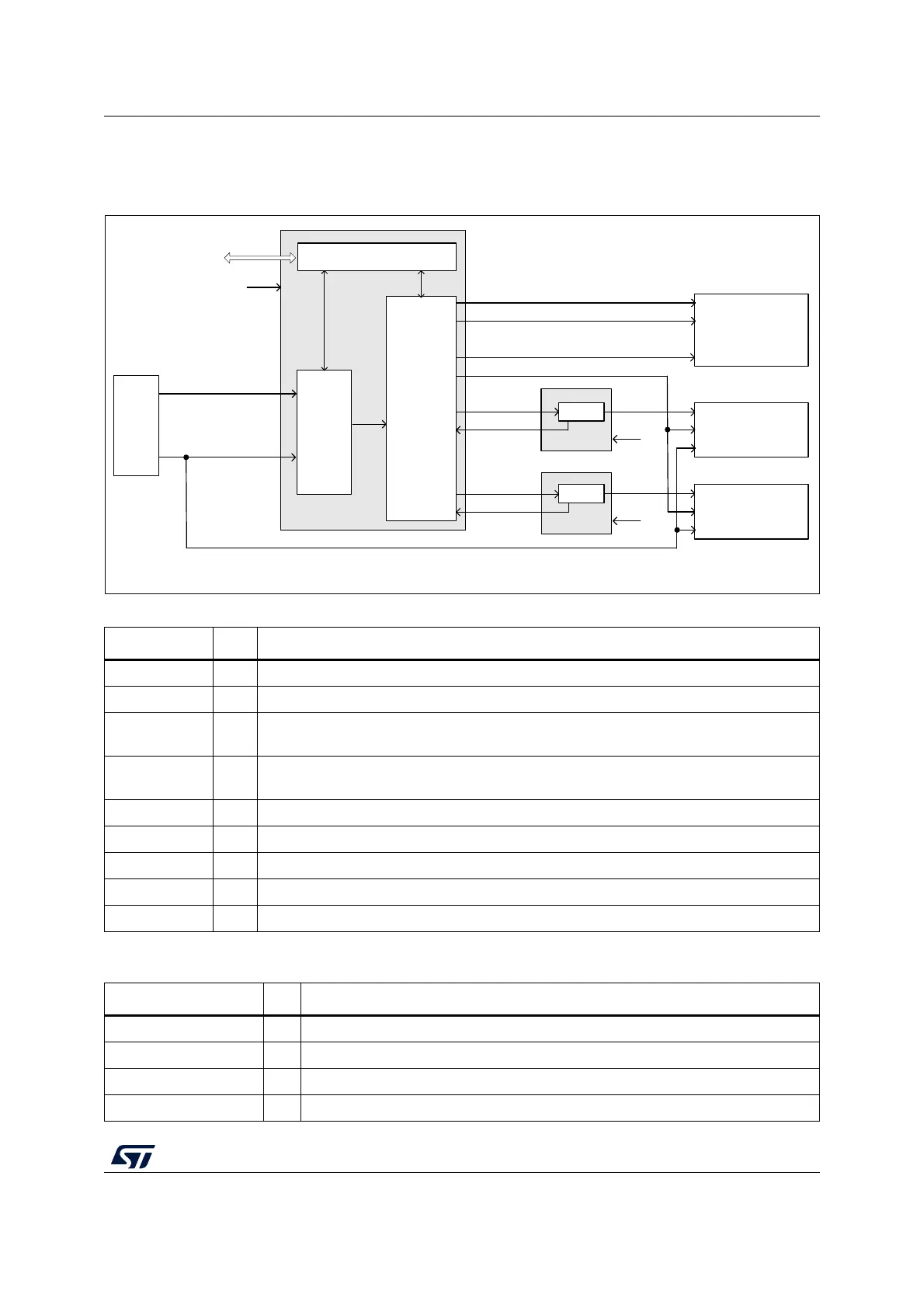

The masking block provides the event input distribution to the different wake-up, interrupt

and event outputs, and the masking of these.

Figure 54. EXTI block diagram

MSv60758V1

EVG

EVG

EXTI

Pulse

Direct event(x) or

configurable event(y)

it_exti_per(y)

(1)

c1_event

c2_evt_exti

c2_wakeup

AHB interface

PWR

CPU1

CPU2

rxev

nvic(x)

rxev

nvic(x)

Peripheral

sys_wakeup

nvic(y)

nvic(y)

Wakeup

Interrupt

Direct event(x)

Pulse

c1_evt_exti

c2_event

c1_evt_rst

c2_evt_rst

hclk

c2_fclk

c1_fclk

c1_wakeup

1) it_exti_per(y) only available for configurable events (y)

Registers

Masking

Event

trigger

Events

Table 91. EXTI pin overview

Pin name I/O Description

AHB interface I/O EXTI register bus interface

hclk I AHB bus clock and EXTI system clock

Configurable

event(y)

I

Asynchronous wake-up events from peripherals which do not have an associated interrupt

and flag in the peripheral

Direct event(x) I

Synchronous and asynchronous wake-up events from peripherals which have an

associated interrupt and flag in the peripheral

it_exti_per (y) O Interrupts to the CPU associated with the configurable event (y)

cn_evt_exti O High-level sensitive event output for the CPUn, synchronous to hclk

cn_evt_rst I Asynchronous reset input to clear cn_evt_exti

sys_wakeup O Asynchronous system wake-up request to PWR for ck_sys and hclk

cn_wakeup O Wake-up request to PWR for the CPUn, synchronous to hclk

Table 92. EVG pin overview

Pin name I/O Description

cn_fclk I CPUn free running clock

cn_evt_in I High-level sensitive events input from EXTI, asynchronous to the CPUn clock

cn_event O Event pulse, synchronous to the CPUn clock

cn_evt_rst O Event reset signal, synchronous to the CPUn clock

Loading...

Loading...