Universal synchronous/asynchronous receiver transmitter (USART/UART) RM0453

1158/1450 RM0453 Rev 5

RS232 RTS and CTS flow control can be enabled independently by writing the RTSE and

CTSE bits to ‘1’ in the USART_CR3 register.

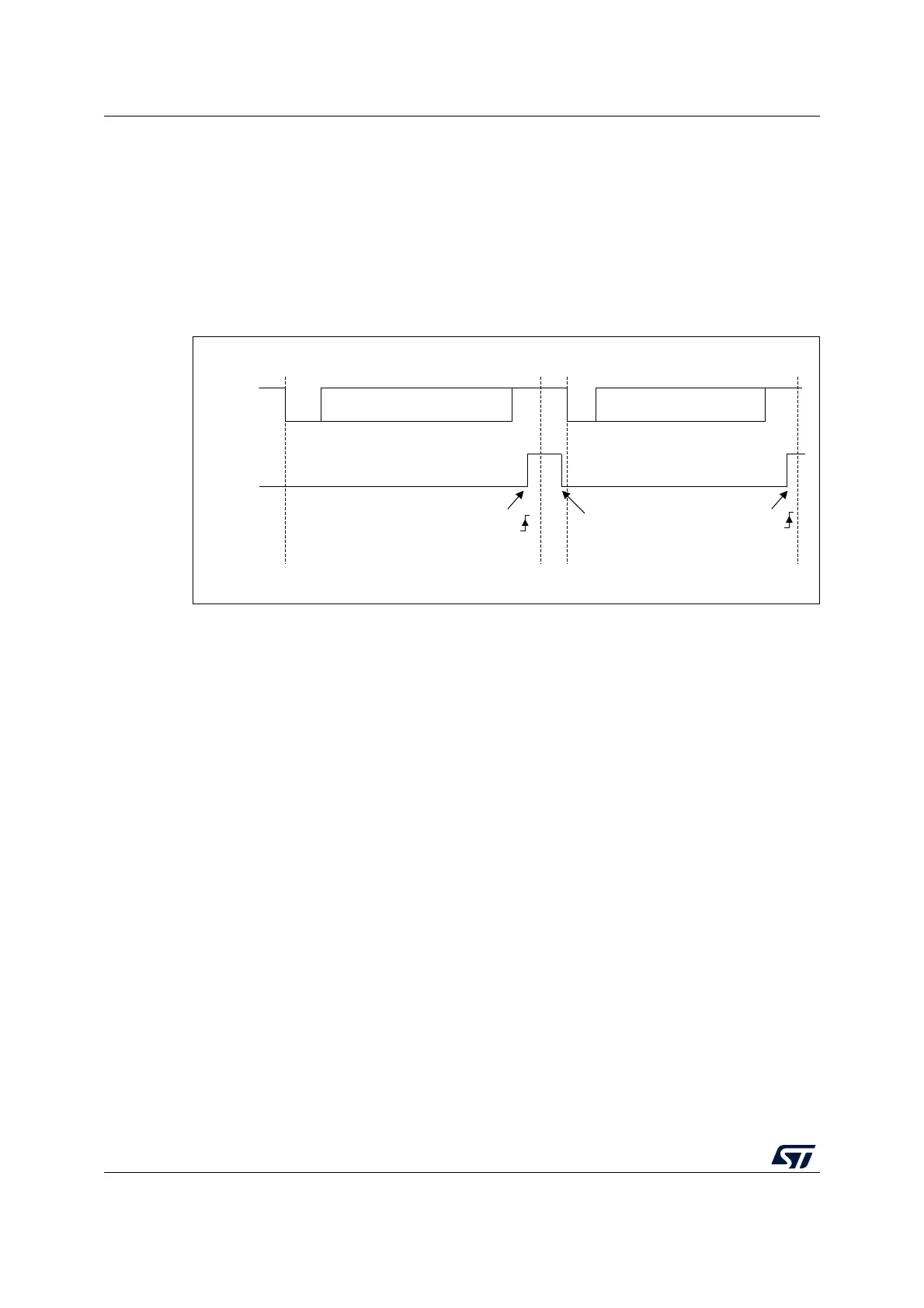

RS232 RTS flow control

If the RTS flow control is enabled (RTSE = 1), then RTS is deasserted (tied low) as long as

the USART receiver is ready to receive a new data. When the receive register is full, RTS is

asserted, indicating that the transmission is expected to stop at the end of the current frame.

Figure 329 shows an example of communication with RTS flow control enabled.

Figure 329. RS232 RTS flow control

Note: When FIFO mode is enabled, RTS is asserted only when RXFIFO is full.

RS232 CTS flow control

If the CTS flow control is enabled (CTSE = 1), then the transmitter checks the CTS input

before transmitting the next frame. If CTS is deasserted (tied low), then the next data is

transmitted (assuming that data is to be transmitted, in other words, if TXE/TXFE = 0), else

the transmission does not occur. When CTS is asserted during a transmission, the current

transmission is completed before the transmitter stops.

When CTSE = 1, the CTSIF status bit is automatically set by hardware as soon as the CTS

input toggles. It indicates when the receiver becomes ready or not ready for communication.

An interrupt is generated if the CTSIE bit in the USART_CR3 register is set. Figure 330

shows an example of communication with CTS flow control enabled.

MSv68794V1

Start

bit

Start

bit

Stop

bit

Idle

Stop

bit

RX

RTS

Data 1 read

Data 2 can now be transmitted

RXNE

RXNE

Data 1 Data 2

Loading...

Loading...