Low-power universal asynchronous receiver transmitter (LPUART) RM0453

1216/1450 RM0453 Rev 5

Note: The data specified in Table 250 may slightly differ in the special case when the received

frames contain some Idle frames of exactly 10-bit times when M bits = ‘00’ (11-bit times

when M = ’01’ or 9- bit times when M = ‘10’).

36.4.9 LPUART multiprocessor communication

It is possible to perform LPUART multiprocessor communications (with several LPUARTs

connected in a network). For instance one of the LPUARTs can be the master, with its TX

output connected to the RX inputs of the other LPUARTs. The others are slaves, with their

respective TX outputs are logically ANDed together and connected to the RX input of the

master.

In multiprocessor configurations it is often desirable that only the intended message

recipient actively receives the full message contents, thus reducing redundant LPUART

service overhead for all non addressed receivers.

The non addressed devices can be placed in Mute mode by means of the muting function.

To use the Mute mode feature, the MME bit must be set in the LPUART_CR1 register.

Note: When FIFO management is enabled and MME is already set, MME bit must not be cleared

and then set again quickly (within two lpuart_ker_ck cycles), otherwise Mute mode might

remain active.

When the Mute mode is enabled:

• none of the reception status bits can be set;

• all the receive interrupts are inhibited;

• the RWU bit in LPUART_ISR register is set to ‘1’. RWU can be controlled automatically

by hardware or by software, through the MMRQ bit in the LPUART_RQR register,

under certain conditions.

The LPUART can enter or exit from Mute mode using one of two methods, depending on

the WAKE bit in the LPUART_CR1 register:

• Idle Line detection if the WAKE bit is reset,

• Address Mark detection if the WAKE bit is set.

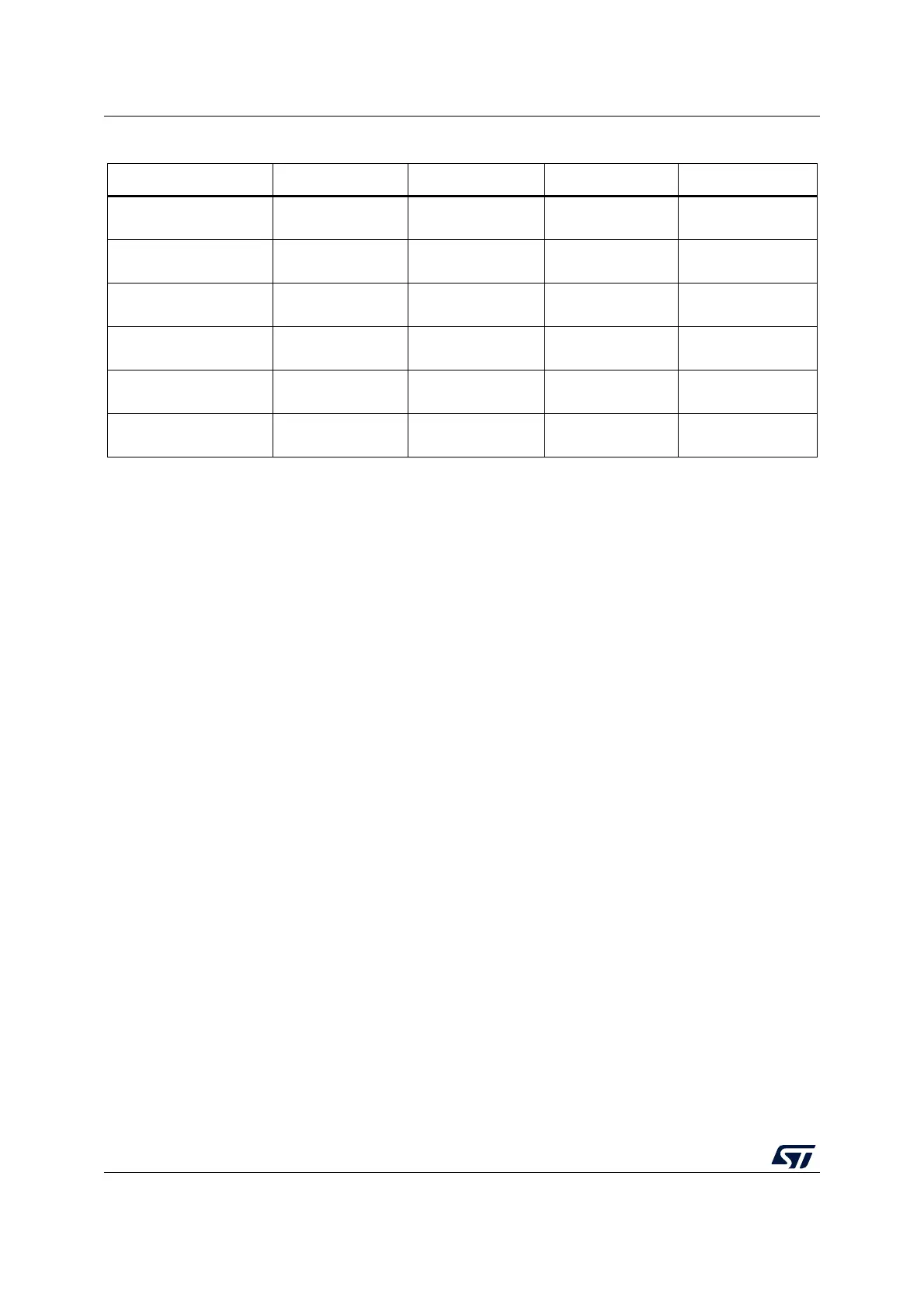

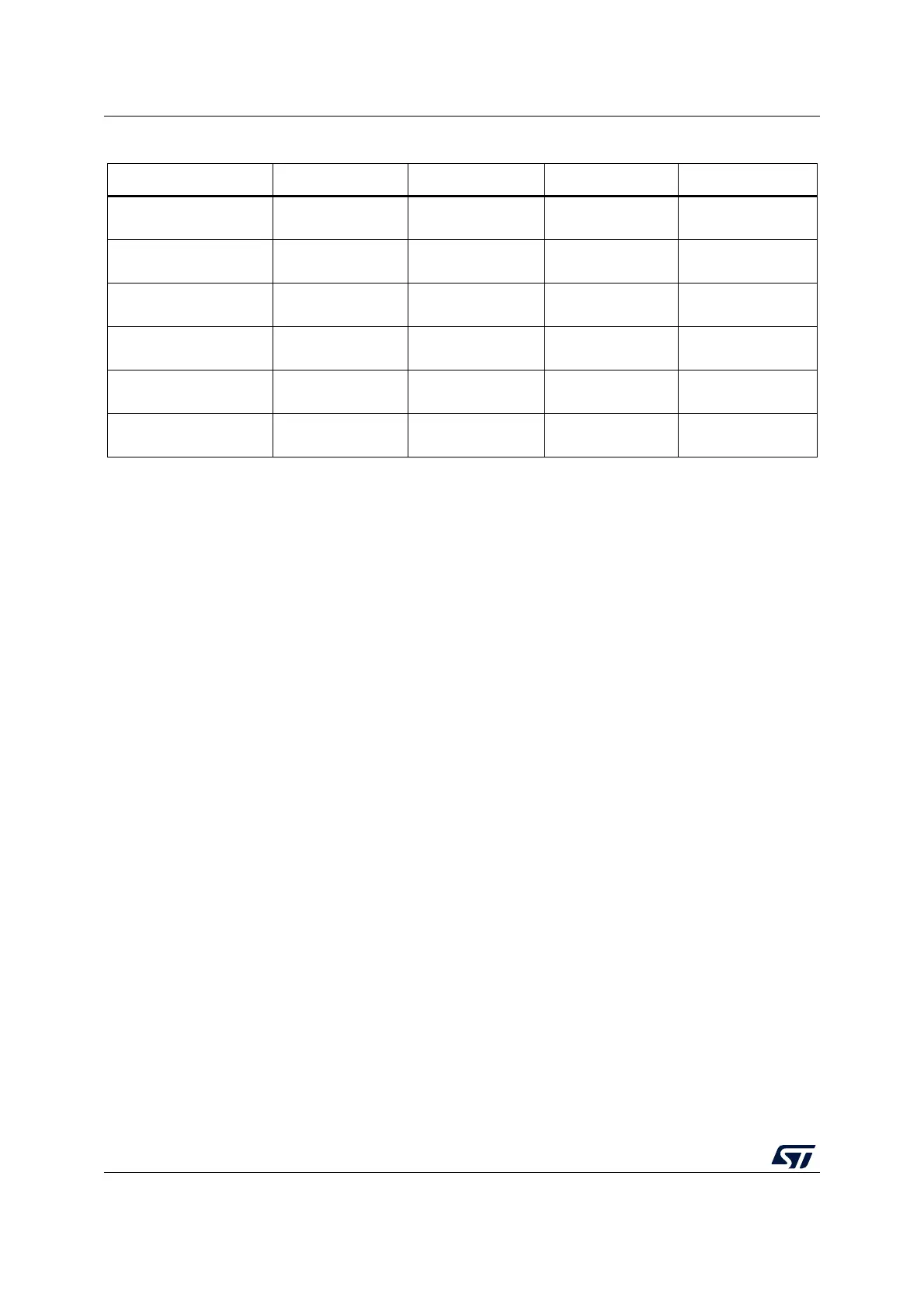

Table 250. Tolerance of the LPUART receiver

M bits 768 < BRR < 1024 1024 < BRR < 2048 2048 < BRR < 4096 4096 ≤ BRR

8 bits (M = 00’), 1 Stop

bit

1.82% 2.56% 3.90% 4.42%

9 bits (M = 01’), 1 Stop

bit

1.69% 2.33% 2.53% 4.14%

7 bits (M = ’10’), 1 Stop

bit

2.08% 2.86% 4.35% 4.42%

8 bits (M = 00’), 2 Stop

bit

2.08% 2.86% 4.35% 4.42%

9 bits (M = 01’), 2 Stop

bit

1.82% 2.56% 3.90% 4.42%

7 bits (M = ’10’), 2 Stop

bit

2.34% 3.23% 4.92% 4.42%

Loading...

Loading...