RM0453 Rev 5 69/1450

RM0453 Memory and bus architecture

70

This example show only a secure and privileged protected memory map. The security and

unprivileged parameters can freely be programmed in any order as detailed below:

• When HDPSA > SFSA> unprivileged watermark > unprivileged write watermark, the

areas appear in the following order:

– Secure privileged hide protection area at the top

– Secure privileged area

– Non-secure privileged area

– Non-secure unprivileged read only area

– Non-secure unprivileged area starting from the memory base address.

• unprivileged write watermark >= unprivileged watermark, the areas appear in the

following order:

– privileged area at the top

– Unprivileged area starting from the memory base address (no unprivileged read

only area in this case)

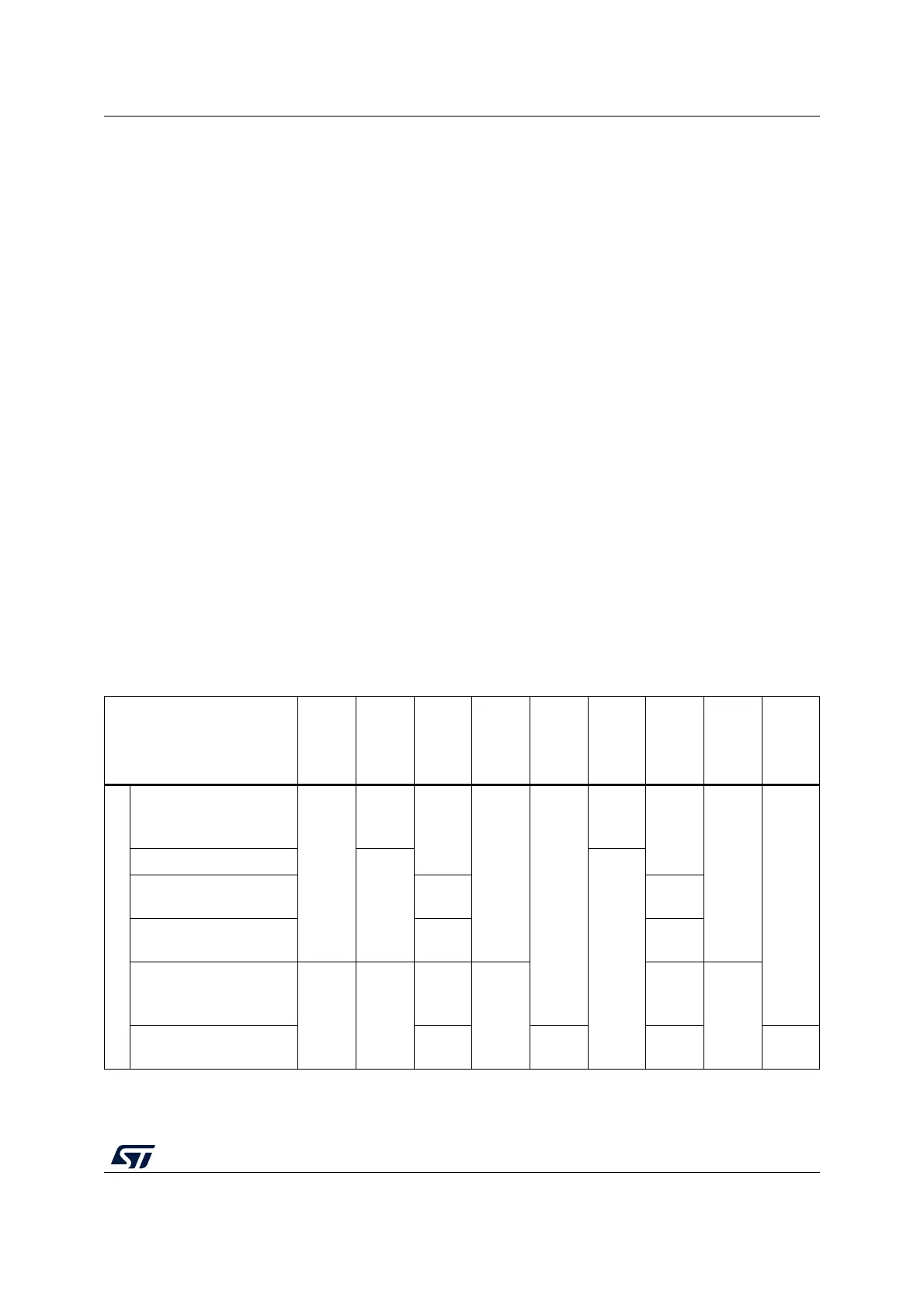

Memory access protection overview

The secure area of the memories have exclusively read, write, execute access only from the

secure CPU2 and secure DMA channels. CPU1 and non-secure DMA channels have no

execute, read, nor write access to these areas.

The non-secure area of the memories grants full read, write, execute access to CPU1 and

all DMA channels. CPU2 has only read and write access to the non-secure areas. CPU2 is

prevented from executing from non-secure areas.

Access rules from the different bus masters and secure, non-secure, privileged and

unprivileged access types to the different memory areas is given in the table below.

Table 3. Memory security and privilege access

SoC level memory area

CPU2 hide

protection

privileged

CPU2

privileged

CPU2

unprivilege

d

CPU1

privileged

CPU1

unprivilege

d

DMA

ch sub-lv

secure priv

DMA

ch sub-lv

secure

DMA

ch sub-lv

non-secure

DMA

ch sub-lv

Non-secure

Flash memory

Hide protection secure

privileged

ex, rd,

wr

no

access

(1)

no

access

(2)

no

access

(2)

no

access

(2)

(rd, wr)

(1)

no

access

(2)

no

access

(2)

no

access

(2)

Secure privileged

ex, rd,

wr

rd, wr

Secure privileged

Unprivileged execution

ex, rd

(3)

rd

Secure unprivileged

ex, rd,

wr

rd, wr

Non-secure privileged

rd, wr rd, wr

no

access

(2)(4)

ex, rd,

wr

no

access

(2)(4)

rd, wr

Non-secure unprivileged rd, wr

ex, rd,

wr

rd, wr rd, wr

Loading...

Loading...