Memory and bus architecture RM0453

70/1450 RM0453 Rev 5

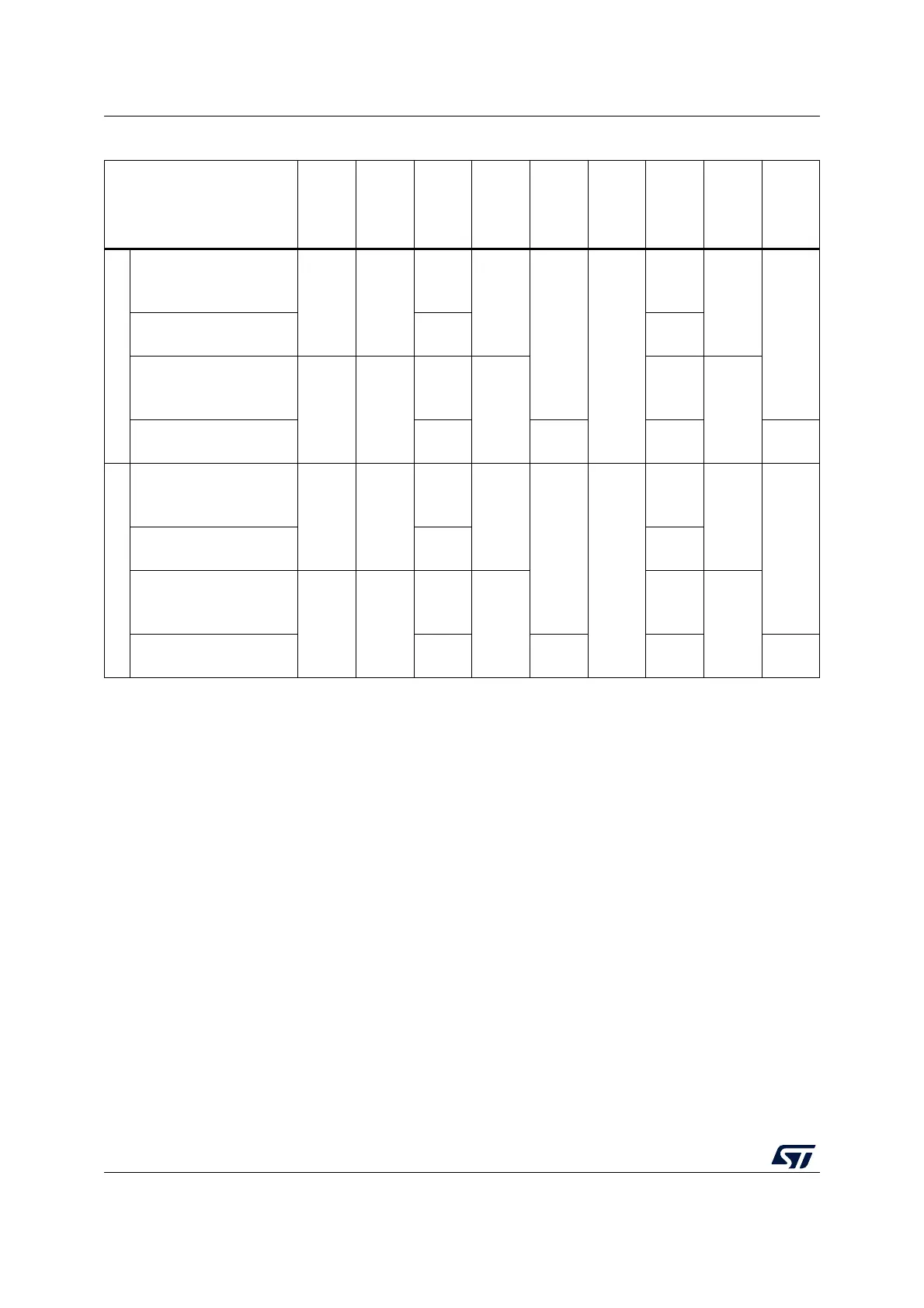

SRAM2

Secure privileged

ex

(5)

,

rd, wr

ex

(5)

,

rd, wr

no

access

(2)

no

access

(6)

no

access

(6)

rd, wr

no

access

(2)(6)

no

access

(2)(6)

no

access

(2)(6)

Secure unprivileged

ex

(5)

,

rd, wr

rd, wr

Non-secure privileged

rd, wr rd, wr

no

access

(2)(4)

ex

(5)

,

rd, wr

no

access

(2)(4)

rd, wr

Non-secure unprivileged rd, wr

ex

(5)

,

rd, wr

rd, wr rd, wr

SRAM1

Secure privileged

ex

(5)

,

rd, wr

ex

(5)

,

rd, wr

no

access

(2)

no

access

(6)

no

access

(6)

rd, wr

no

access

(2)

no

access

(2)

no

access

(2)

Secure unprivileged

ex

(5)

,

rd, wr

rd, wr

Non-secure privileged

rd, wr rd, wr

no

access

(2)(4)

ex

(5)

,

rd, wr

no

access

(2)(4)

rd, wr

Non-secure unprivileged rd, wr

ex

(5)

,

rd, wr

rd, wr rd, wr

1. Access to the hide protection secure privileged area is disabled by flash memory hide protection secure privileged

HDPADIS bit.

2. Read access returns a zero value, write access is ignored and, in both cases, an illegal access event is generated.

3. The secure privileged and unprivileged, read and execute protected pages cannot be written by a secure unprivileged

access. However it can be erased by a secure unprivileged page erase.

4. Privileged area start address < secure area start address.

5. Execution from SRAM1 and SRAM2 can be disabled by the execute never feature available from the MPU in the respective

CPU.

6. Read access returns a zero value, write access is ignored and, in both cases, an illegal access event is generated. When

RDP level is 1 and CPU1 boots from SRAM1, SRAM2 is locked and no illegal access event is generated.

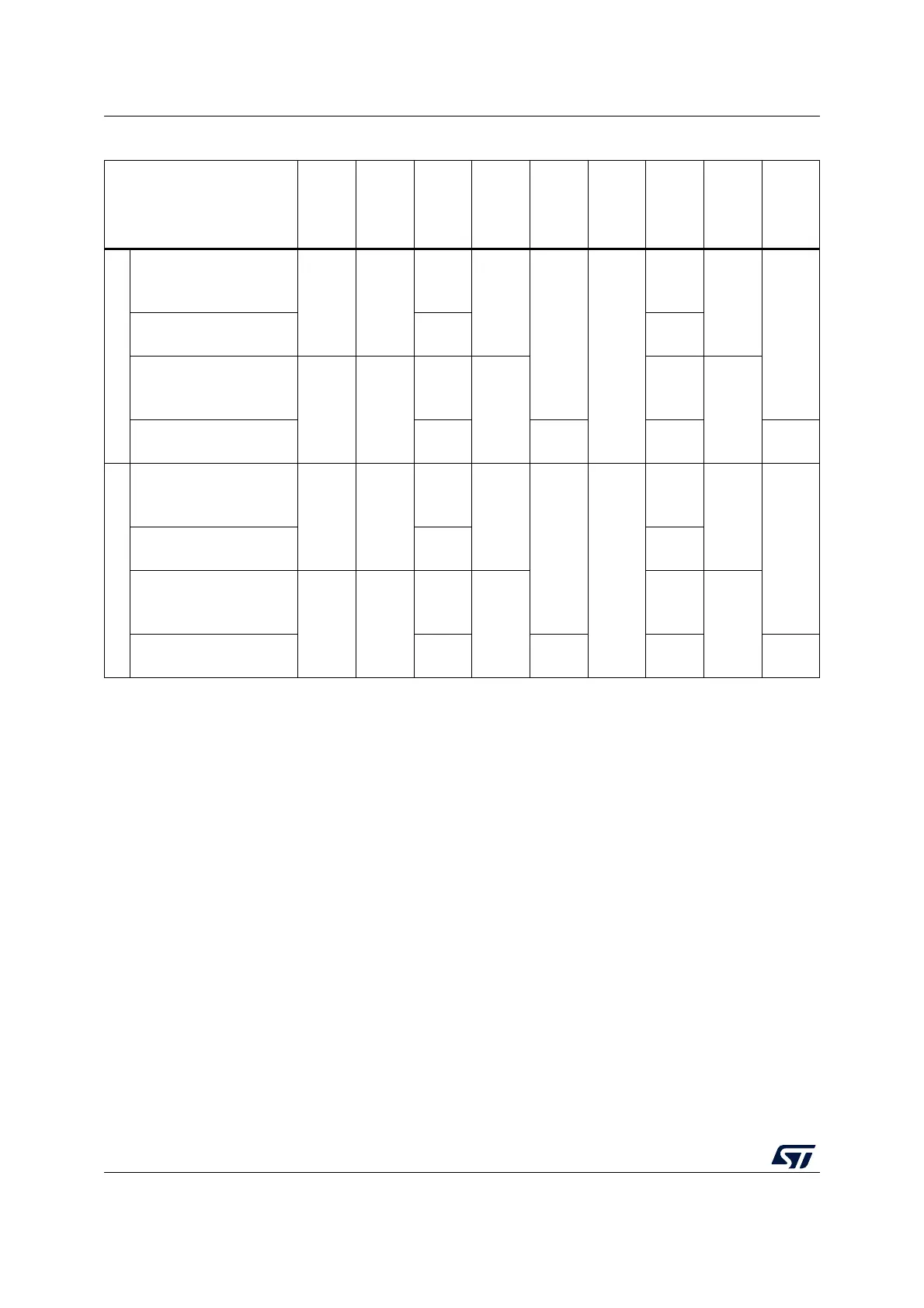

Table 3. Memory security and privilege access (continued)

SoC level memory area

CPU2 hide

protection

privileged

CPU2

privileged

CPU2

unprivilege

d

CPU1

privileged

CPU1

unprivilege

d

DMA

ch sub-lv

secure priv

DMA

ch sub-lv

secure

DMA

ch sub-lv

non-secure

DMA

ch sub-lv

Non-secure

Loading...

Loading...