Inter-integrated circuit (I2C) interface RM0453

1080/1450 RM0453 Rev 5

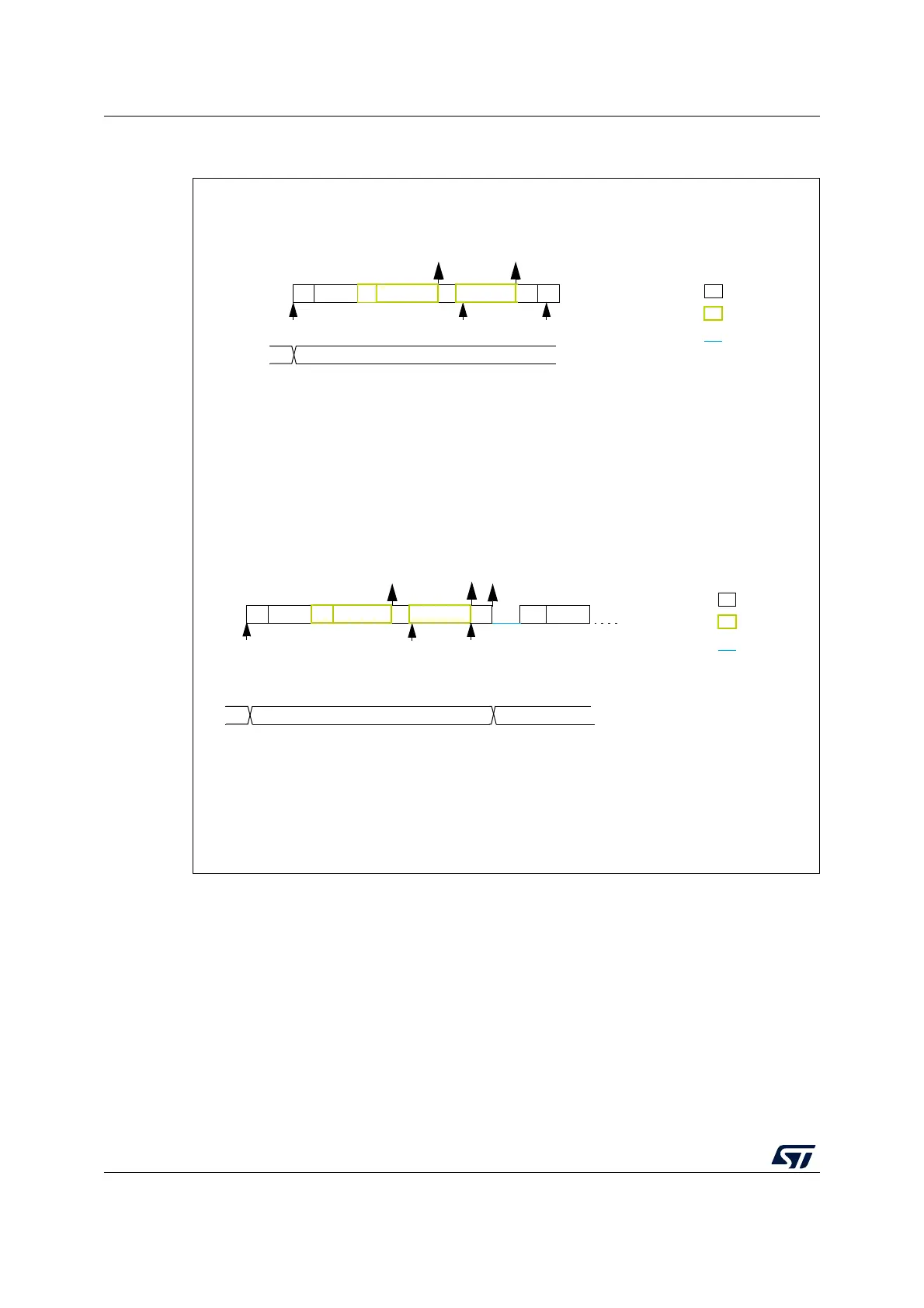

Figure 298. Transfer bus diagrams for I2C master receiver

(mandatory events only)

34.4.10 I2C_TIMINGR register configuration examples

The following tables provide examples of how to program the I2C_TIMINGR to obtain

timings compliant with the I

2

C specification. To get more accurate configuration values, use

the STM32CubeMX tool (I2C Configuration window).

Example I2C master receiver 2 bytes, automatic end mode (STOP)

INIT: program Slave address, program NBYTES = 2, AUTOEND=1, set START

EV1: RXNE ISR: rd data1

EV2: RXNE ISR: rd data2

A

RXNE RXNE

NBYTES

legend:

transmission

reception

SCL stretch

EV1

xx 2

INIT

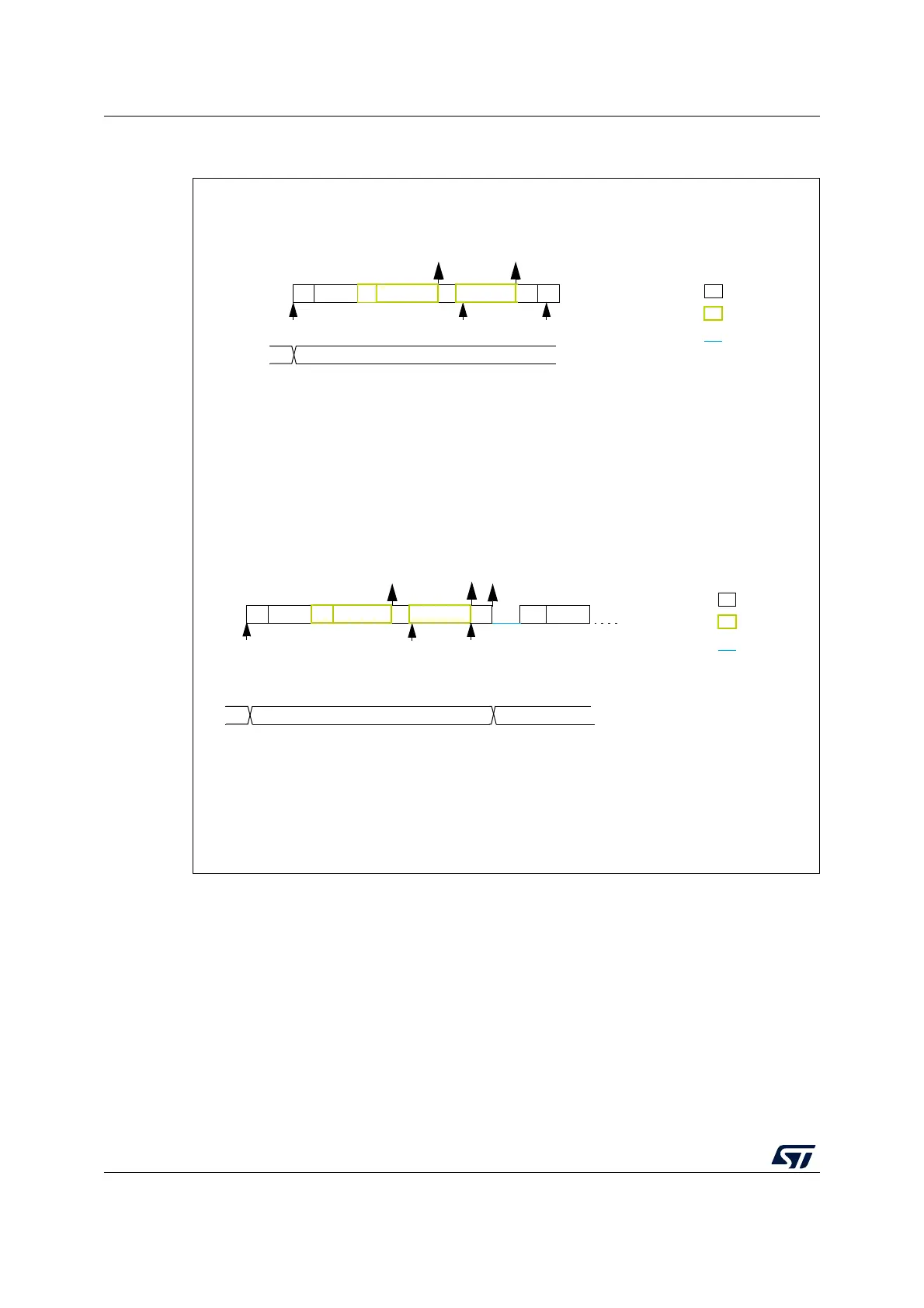

Example I2C master receiver 2 bytes, software end mode (RESTART)

INIT: program Slave address, program NBYTES = 2, AUTOEND=0, set START

EV1: RXNE ISR: rd data1

EV2: RXNE ISR: read data2

EV3: TC ISR: program Slave address, program NBYTES = N, set START

A

RXNE RXNE

NBYTES

legend:

transmission

reception

SCL stretch

EV1 EV2

xx

INIT

N

EV2

2

TC

AddressS A data1 data2 NA ReS Address

S Address A data1 data2 NA P

Loading...

Loading...