Extended interrupts and event controller (EXTI) RM0453

516/1450 RM0453 Rev 5

16.6.3 EXTI software interrupt event register (EXTI_SWIER1)

Address offset: 0x008

Reset value: 0x0000 0000

Contains only register bits for configurable events.

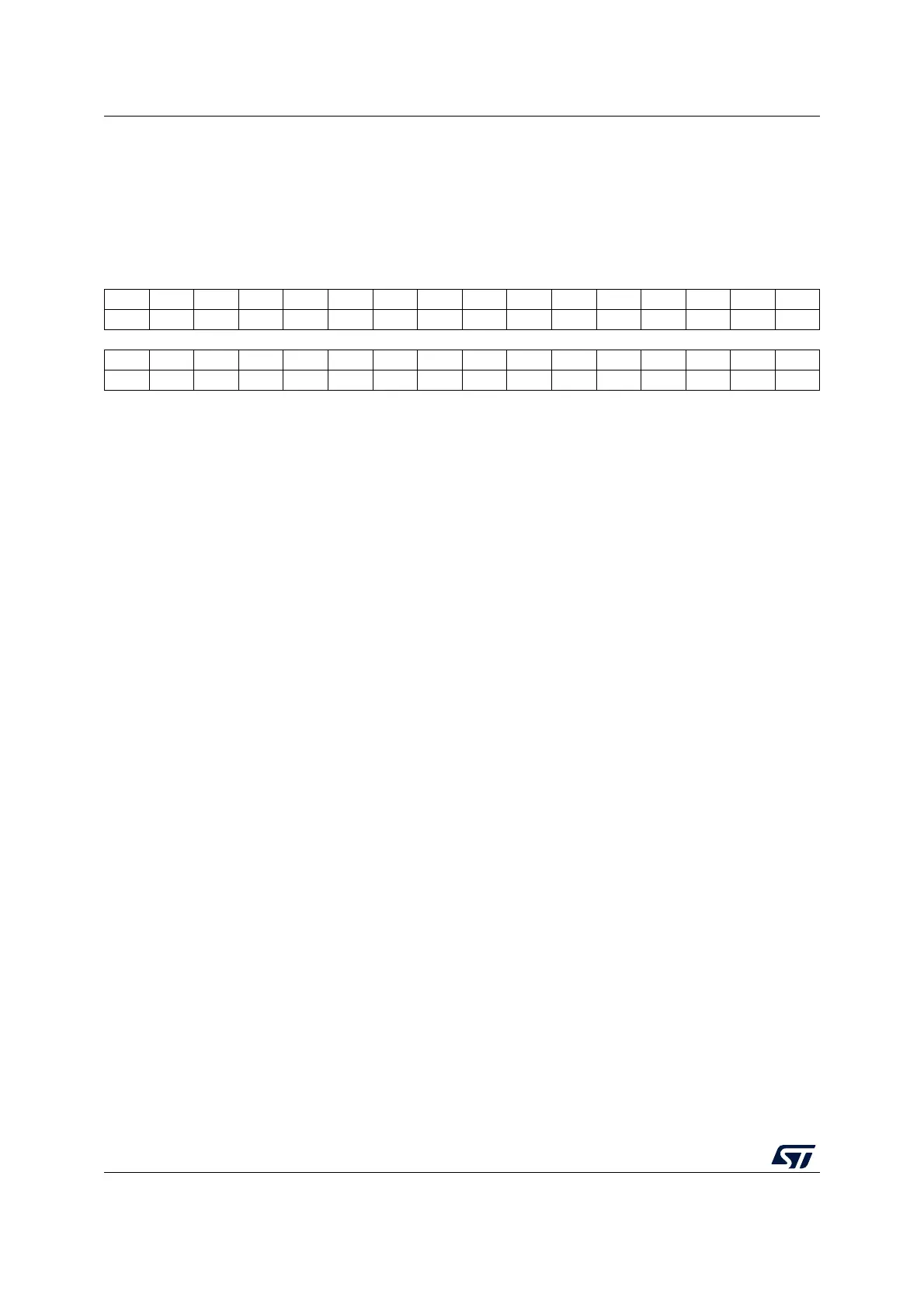

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16

Res. Res. Res. Res. Res. Res. Res. Res. Res. SWI22 SWI21 Res. Res. Res. Res. SWI16

rw rw rw

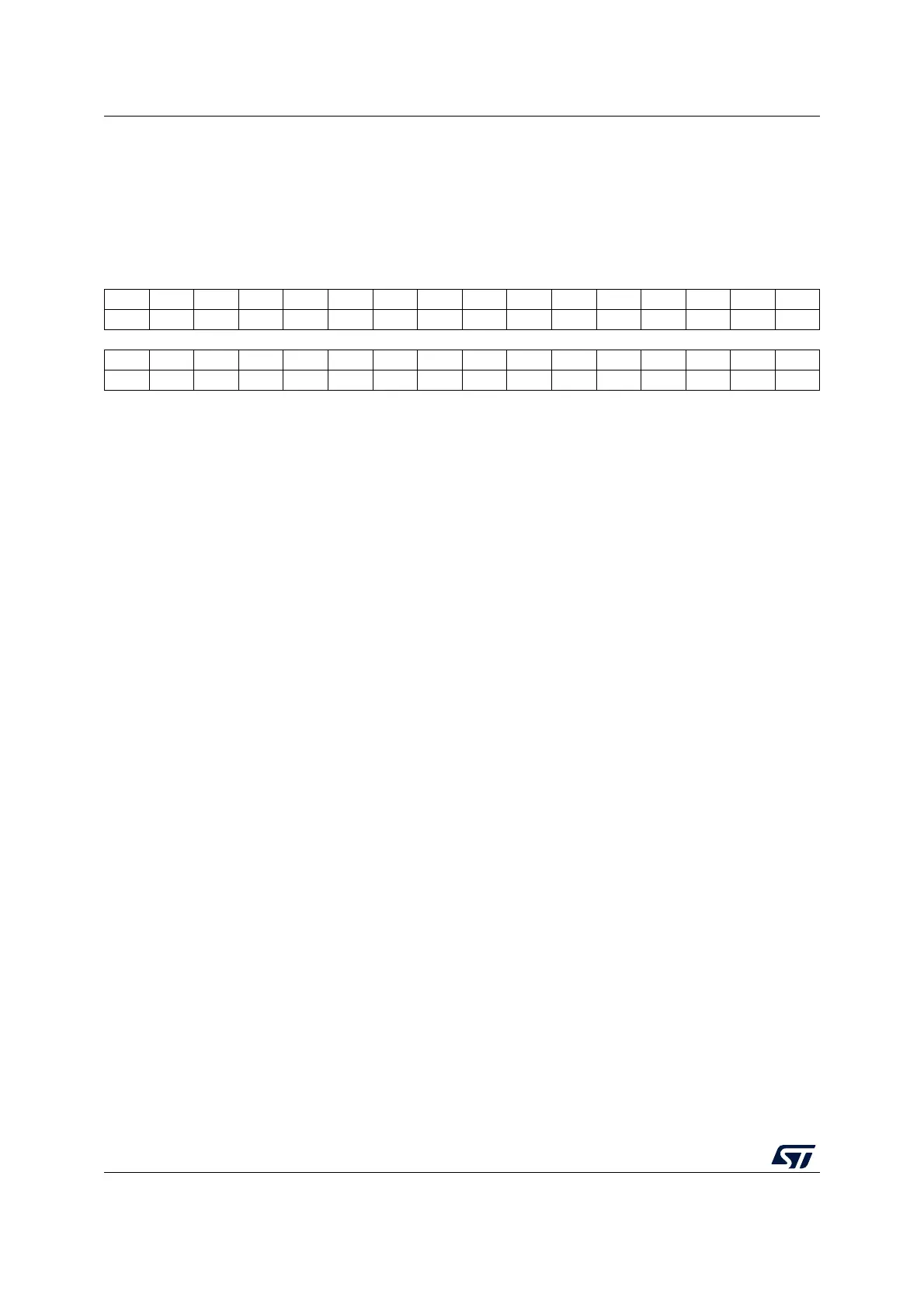

1514131211109876543210

SWI15 SWI14 SWI13 SWI12 SWI11 SWI10 SWI9 SWI8 SWI7 SWI6 SWI5 SWI4 SWI3 SWI2 SWI1 SWI0

rw rw rw rw rw rw rw rw rw rw rw rw rw rw rw rw

Bits 31:23 Reserved, must be kept at reset value.

Bit 22 SWI22: Software interrupt on line 22

A software interrupt is generated independently from the setting in EXTI_RTSR and

EXTI_FTSR. This bit always returns 0 when read.

0: Writing 0 has no effect.

1: Writing 1 to this bit triggers an event on line 22.

This bit is automatically cleared by hardware.

Bit 21 SWI21: Software interrupt on line 21

Bits 20:17 Reserved, must be kept at reset value.

Bit 16 SWI16: Software interrupt on line 16

Bit 15 SWI15: Software interrupt on line 15

Bit 14 SWI14: Software interrupt on line 14

Bit 13 SWI13: Software interrupt on line 13

Bit 12 SWI12: Software interrupt on line 12

Bit 11 SWI11: Software interrupt on line 11

Bit 10 SWI10: Software interrupt on line 10

Bit 9 SWI9: Software interrupt on line 9

Bit 8 SWI8: Software interrupt on line 8

Bit 7 SWI7: Software interrupt on line 7

Bit 6 SWI6: Software interrupt on line 6

Bit 5 SWI5: Software interrupt on line 5

Bit 4 SWI4: Software interrupt on line 4

Bit 3 SWI3: Software interrupt on line 3

Bit 2 SWI2: Software interrupt on line 2

Bit 1 SWI1: Software interrupt on line 1

Bit 0 SWI0: Software interrupt on line 0

Loading...

Loading...