Section 11: TSP command reference Model 2601B-PULSE System SourceMeter Instrument Reference Manual

11-322 2601B-PULSE-901-01A April 2020

Example

questionableRegister = status.questionable.instrument.smua.CAL +

status.questionable.instrument.smua.UO

status.questionable.instrument.smua.enable = questionableRegister

Uses constants to set bits B8 and bit B9 of the questionable status SMU A summary enable register.

Example

questionableRegister = 768

status.questionable.instrument.smua.enable = questionableRegister

Uses the decimal value to set bits B8 and bit B9 of the questionable status SMU A summary enable register.

Also see

Questionable Status Registers (on page 15-13)

status.operation.* (on page 11-281)

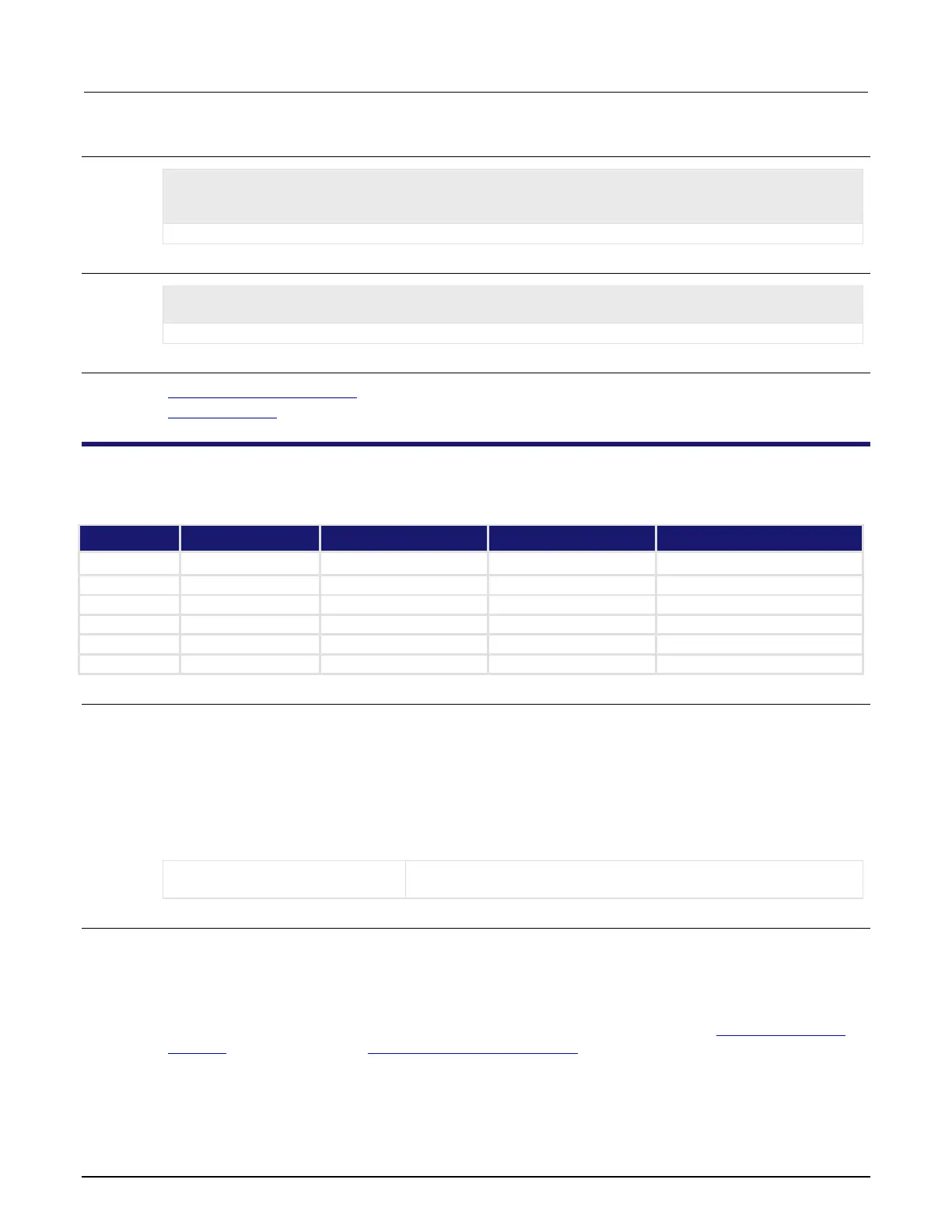

status.questionable.over_temperature.*

This attribute contains the questionable status over temperature summary register set.

Usage

questionableRegister = status.questionable.over_temperature.condition

questionableRegister = status.questionable.over_temperature.enable

questionableRegister = status.questionable.over_temperature.event

questionableRegister = status.questionable.over_temperature.ntr

questionableRegister = status.questionable.over_temperature.ptr

status.questionable.over_temperature.enable = questionableRegister

status.questionable.over_temperature.ntr = questionableRegister

status.questionable.over_temperature.ptr = questionableRegister

The status of the questionable status over temperature summary

register; a zero (0) indicates no bits set (also send 0 to clear all bits)

Details

These attributes are used to read or write to the questionable status over temperature summary

registers. Reading a status register returns a value. The binary equivalent of the returned value

indicates if a register bit is set. The least significant bit of the binary number is bit B0, and the most

significant bit is bit B15.

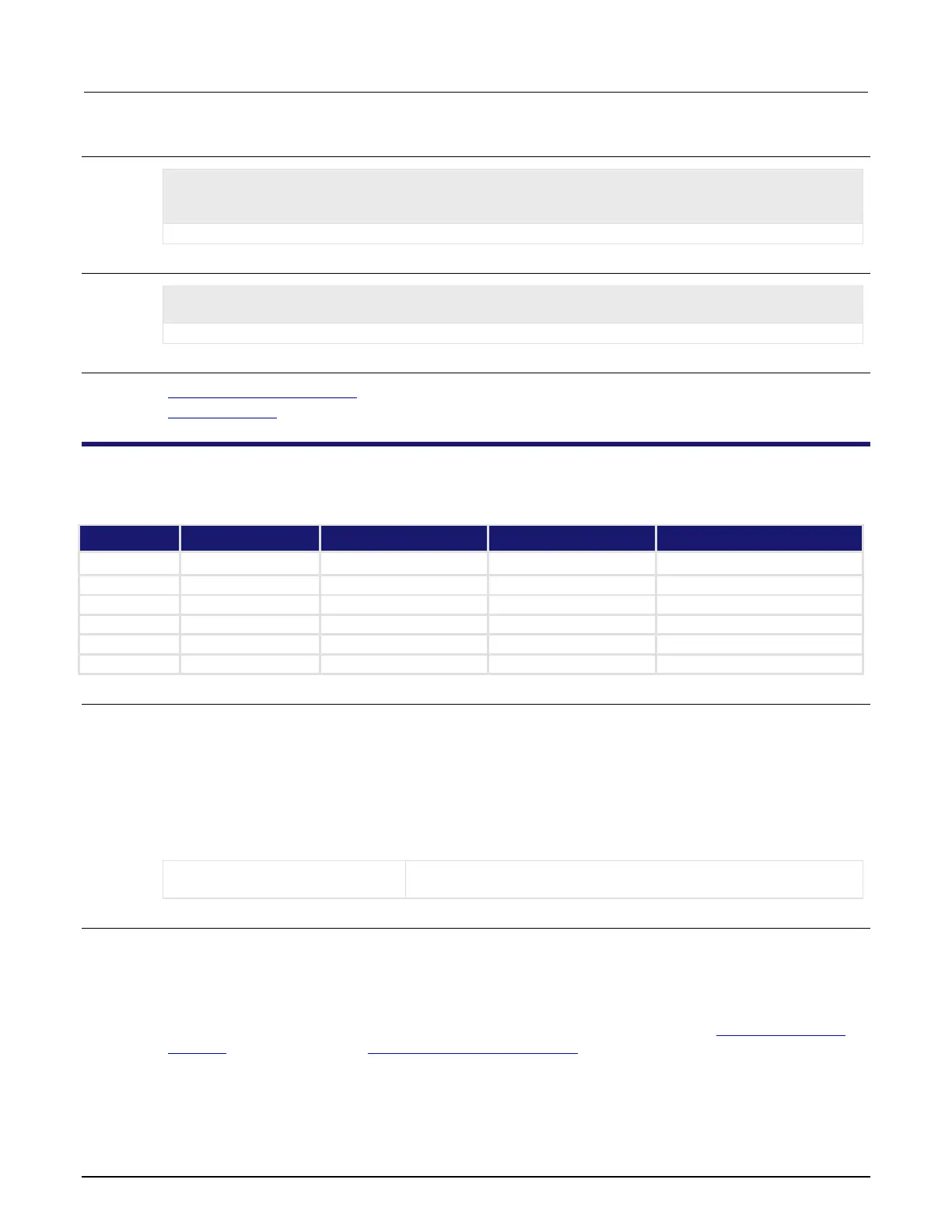

For information about .condition, .enable, .event, .ntr, and .ptr registers, refer to Status register set

contents (on page 15-1) and Enable and transition registers (on page 15-19). The individual bits of

this register are defined in the following table.

Loading...

Loading...