Debug support (DBG) RM0453

1356/1450 RM0453 Rev 5

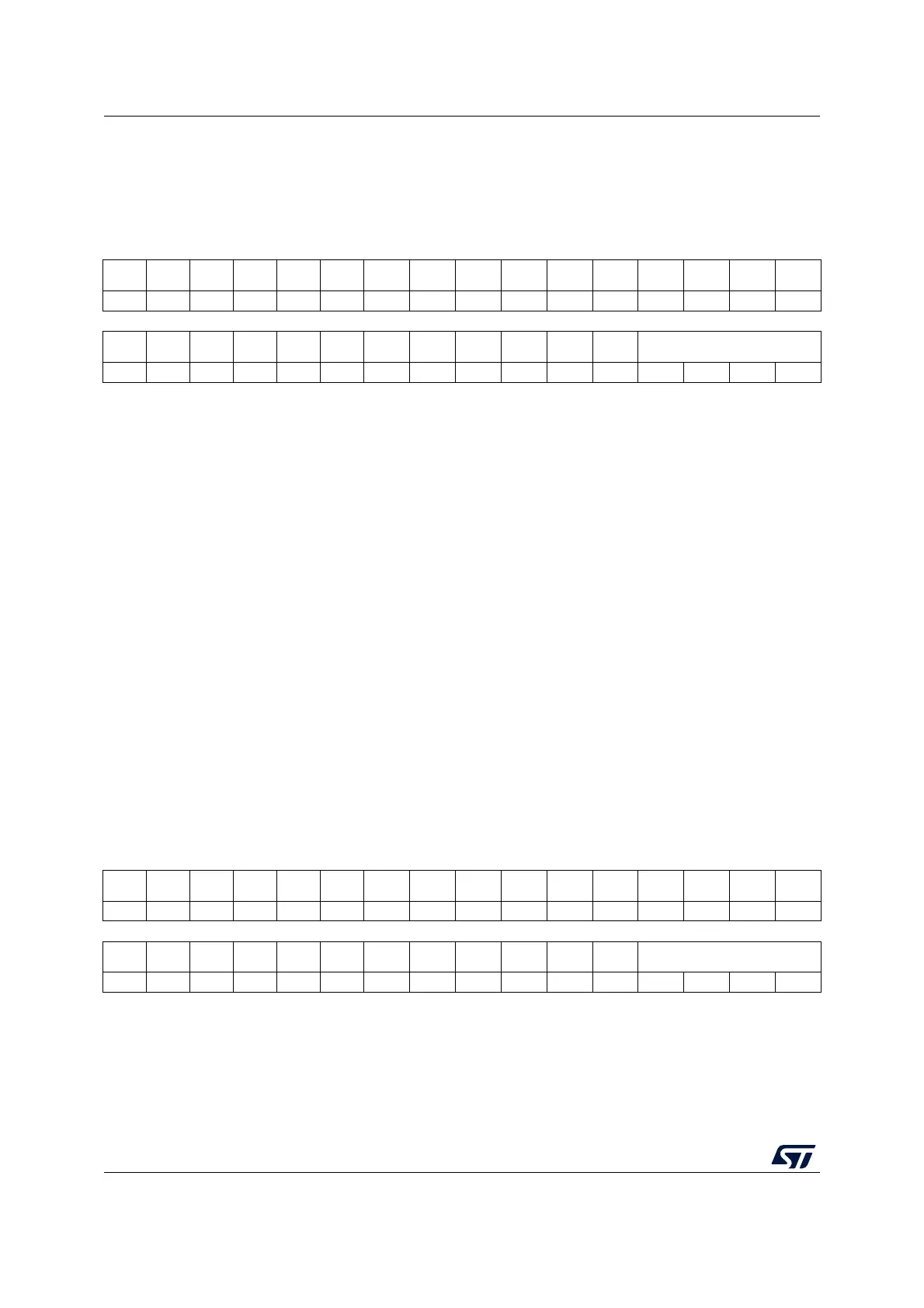

CTI application trigger set register (CTI_APPSETR)

Address offset: 0x014

Reset value: 0x0000 0000

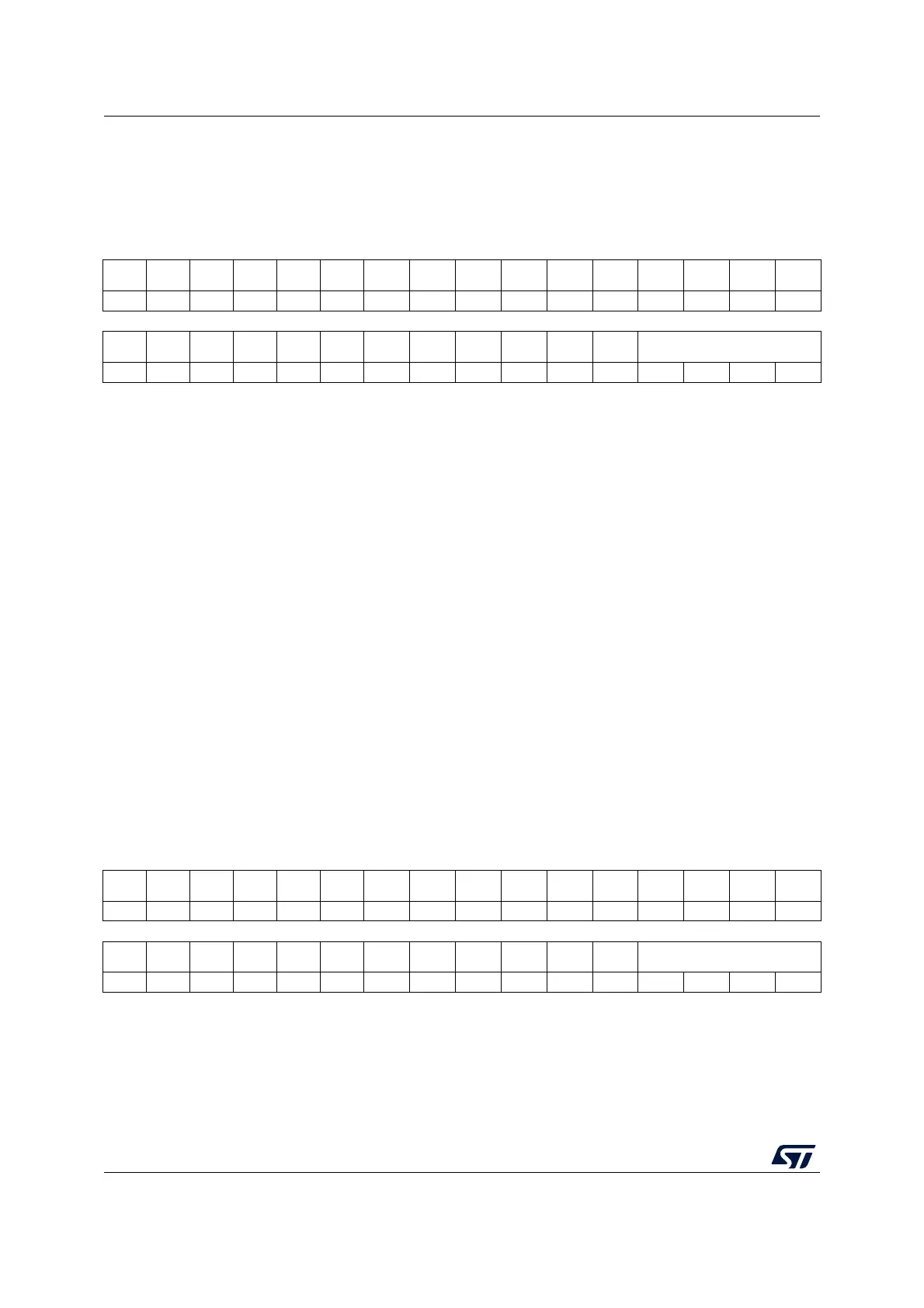

CTI application trigger clear register (CTI_APPCLEAR)

Address offset: 0x018

Reset value: 0x0000 0000

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16

Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res.

1514131211109876543210

Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. APPSET[3:0]

rw rw rw rw

Bits 31:4 Reserved, must be kept at reset value.

Bits 3:0 APPSET[3:0]: channel event setting

Read:

XXX0: Channel 0 event inactive

XXX1: Channel 0 event active

XX0X: Channel 1 event inactive

XX1X: Channel 1 event active

X0XX: Channel 2 event inactive

X1XX: Channel 2 event active

0XXX: Channel 3 event inactive

1XXX: Channel 3 event active

Write:

0000: No effect

XXX1: Sets event on Channel 0.

XX1X: Sets event on Channel 1.

X1XX: Sets event on Channel 2.

1XXX: Sets event on Channel 3.

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16

Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res.

1514131211109876543210

Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. APPCLEAR[3:0]

wwww

Loading...

Loading...