RM0453 Rev 5 1357/1450

RM0453 Debug support (DBG)

1435

CTI application pulse register (CTI_APPPULSER)

Address offset: 0x01C

Reset value: 0x0000 0000

w

CTI trigger in x enable register (CTI_INENRx)

Address offset: 0x020 + 0x004 * x, (x = 0 to 7)

Reset value: 0x0000 0000

Bits 31:4 Reserved, must be kept at reset value.

Bits 3:0 APPCLEAR[3:0]: channel event clearing

0000: No effect

XXX1: Clears event on Channel 0.

XX1X: Clears event on Channel 1.

X1XX: Clears event on Channel 2.

1XXX: Clears event on Channel 3.

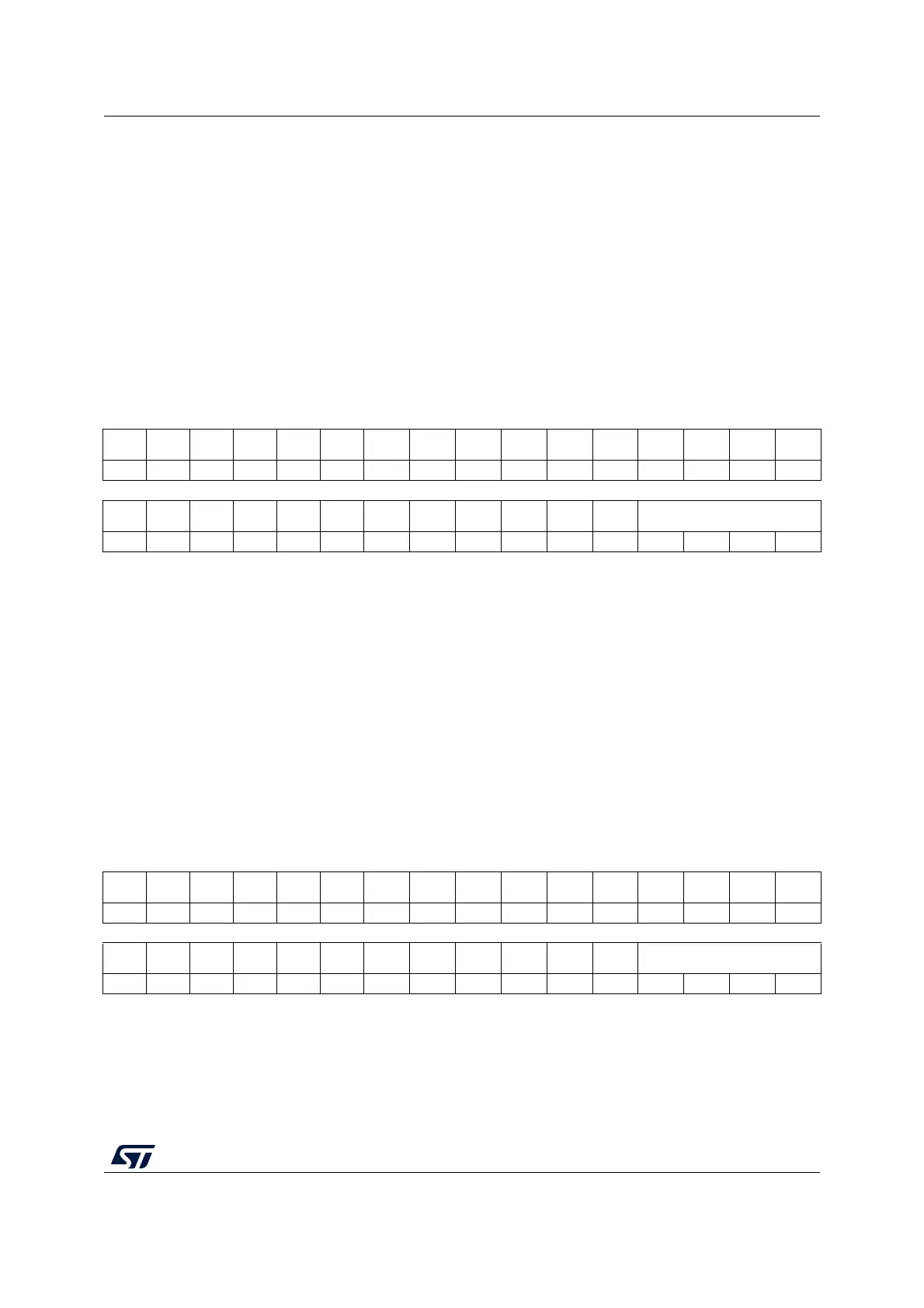

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16

Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res.

1514131211109876543210

Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. APPPULSE[3:0]

wwww

Bits 31:4 Reserved, must be kept at reset value.

Bits 3:0 APPPULSE[3:0]: pulse channel event

This register clears itself immediately.

0000: No effect

XXX1: Generates pulse on Channel 0.

XX1X: Generates pulse on Channel 1.

X1XX: Generates pulse on Channel 2.

1XXX: Generates pulse on Channel 3.

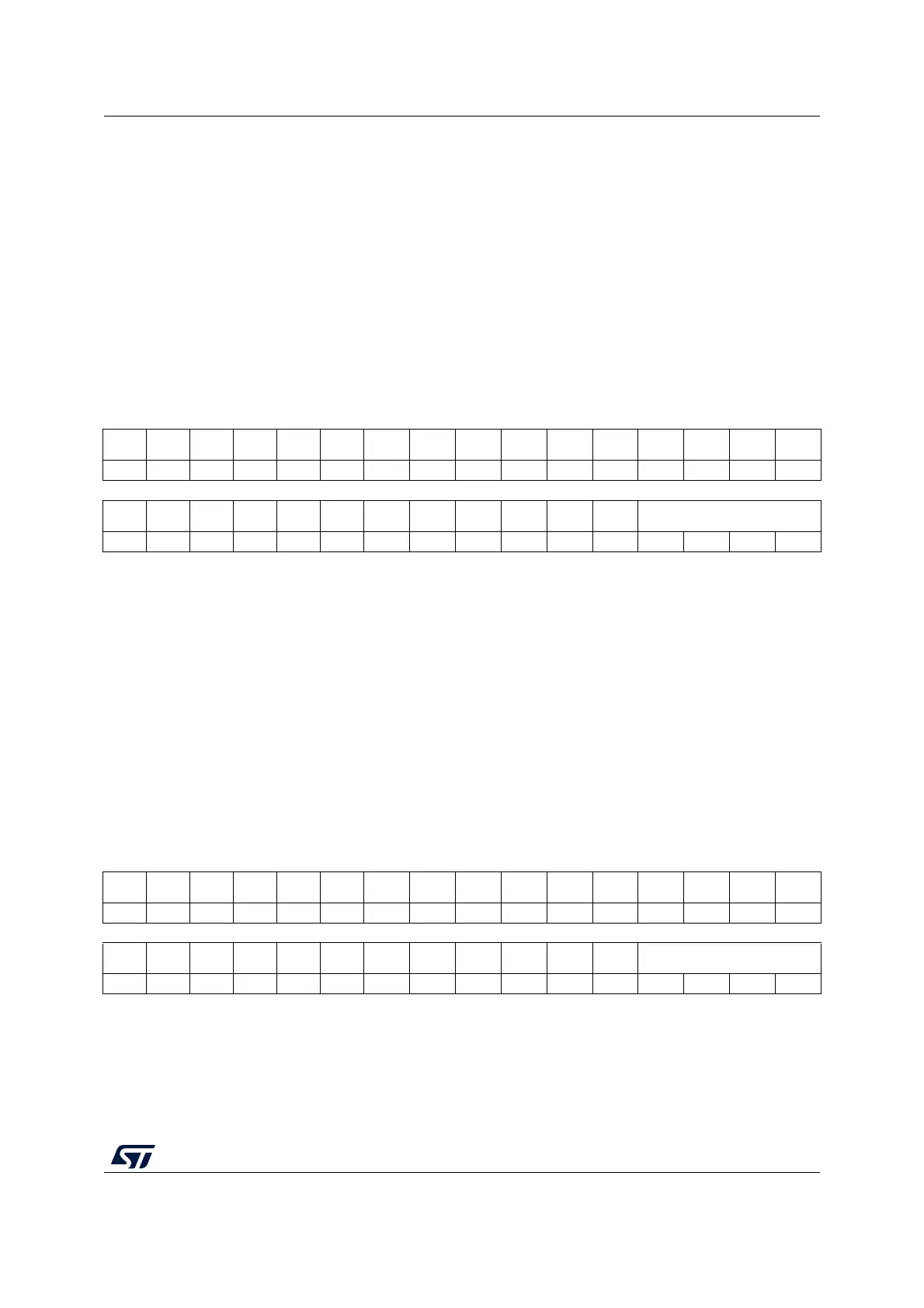

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16

Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res.

1514131211109876543210

Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. TRIGINEN[3:0]

rw rw rw rw

Loading...

Loading...