Debug support (DBG) RM0453

1358/1450 RM0453 Rev 5

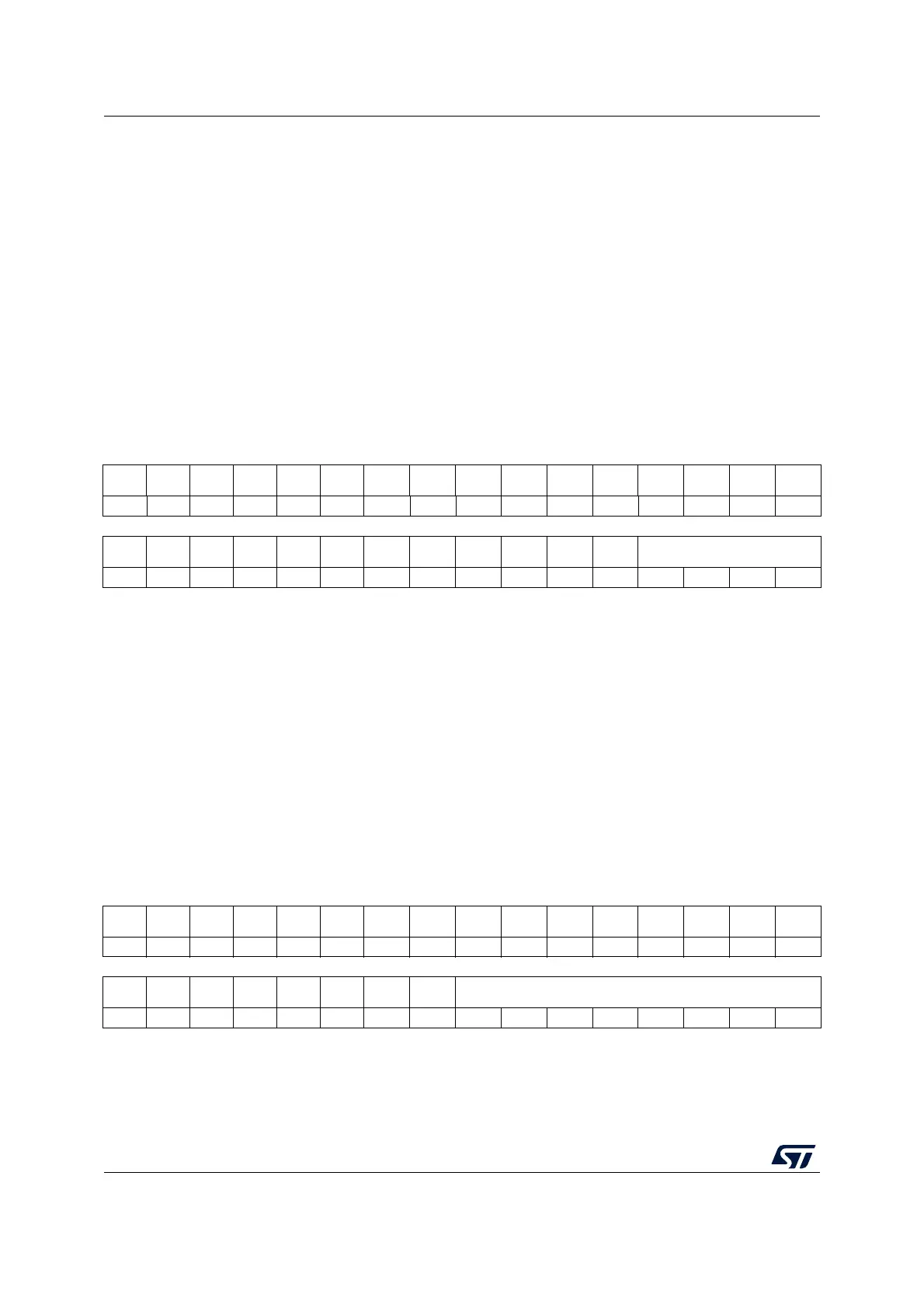

CTI trigger out x enable register (CTI_OUTENRx)

Address offset: 0x0A0 + 0x004 * x, (x = 0 to 7)

Reset value: 0x0000 0000

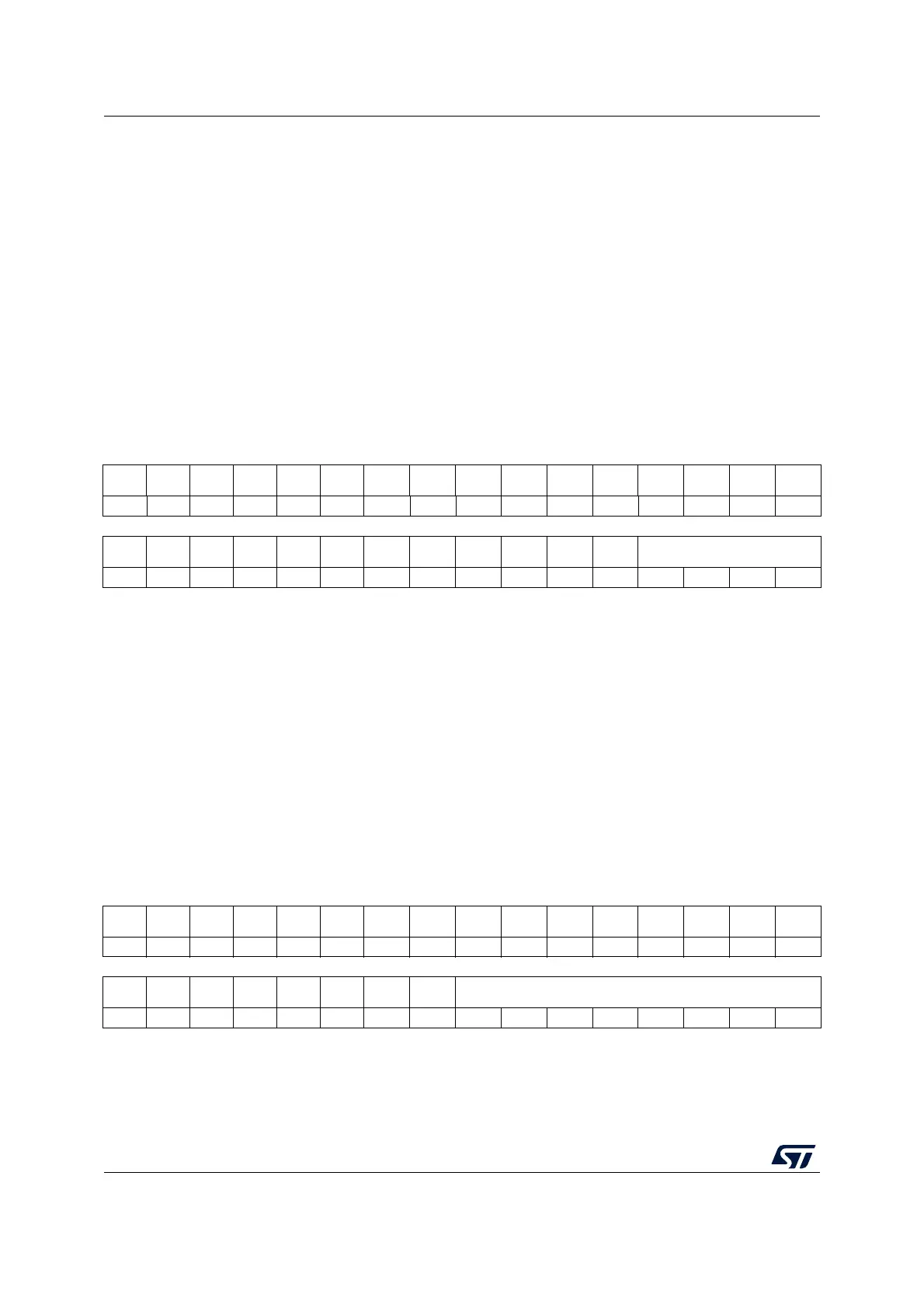

CTI trigger in status register (CTI_TRGISTSR)

Address offset: 0x130

Reset value: 0x0000 0000

Bits 31:4 Reserved, must be kept at reset value.

Bits 3:0 TRIGINEN[3:0]: cross trigger event enable/disable

Enables or disables a cross trigger event on each of the four channels when CTITRIGINx is

activated (x = 0 to 7).

0000: Trigger does not generate events on any channel.

XXX1: Trigger n generates events on Channel 0.

XX1X: Trigger n generates events on Channel 1.

X1XX: Trigger n generates events on Channel 2.

1XXX: Trigger n generates events on Channel 3.

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16

Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res.

1514131211109876543210

Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. TRIGOUTEN[3:0]

rw rw rw rw

Bits 31:4 Reserved, must be kept at reset value.

Bits 3:0 TRIGOUTEN[3:0]: For each channel, defines whether an event on that channel generates a

trigger on CTITRIGOUTx (x = 0 to 7).

0000: Channel events do not generate triggers on any trigger output.

XXX1: Channel 0 events generate triggers on Trigger output n.

XX1X: Channel 1 events generate triggers on Trigger output n.

X1XX: Channel 2 events generate triggers on Trigger output n.

1XXX: Channel 3 events generate triggers on Trigger output n.

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16

Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res.

1514131211109876543210

Res. Res. Res. Res. Res. Res. Res. Res. TRIGINSTATUS[7:0]

rrrrrrrr

Loading...

Loading...