Debug support (DBG) RM0453

1360/1450 RM0453 Rev 5

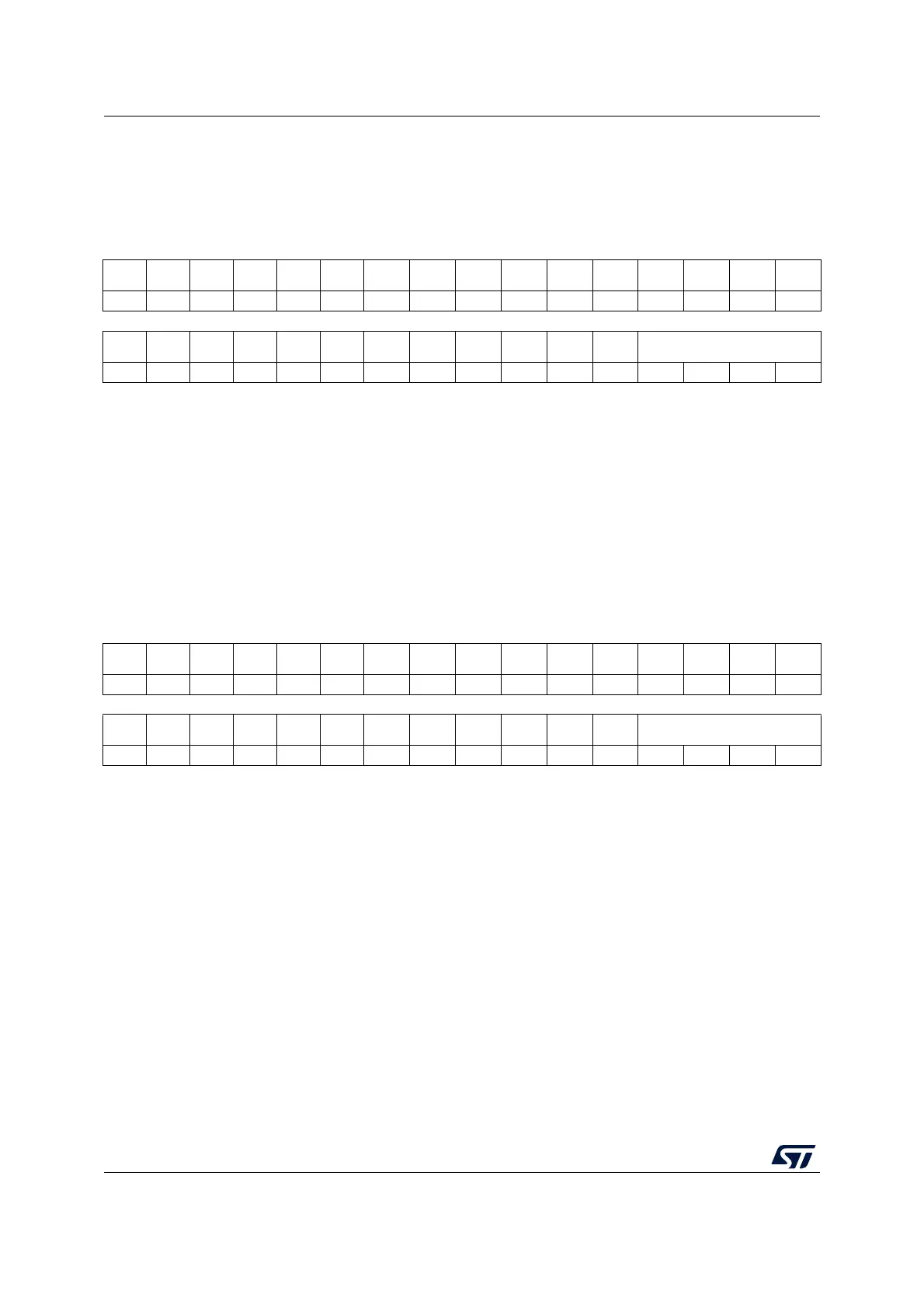

CTI channel out status register (CTI_CHOUTSTSR)

Address offset: 0x13C

Reset value: 0x0000 0000

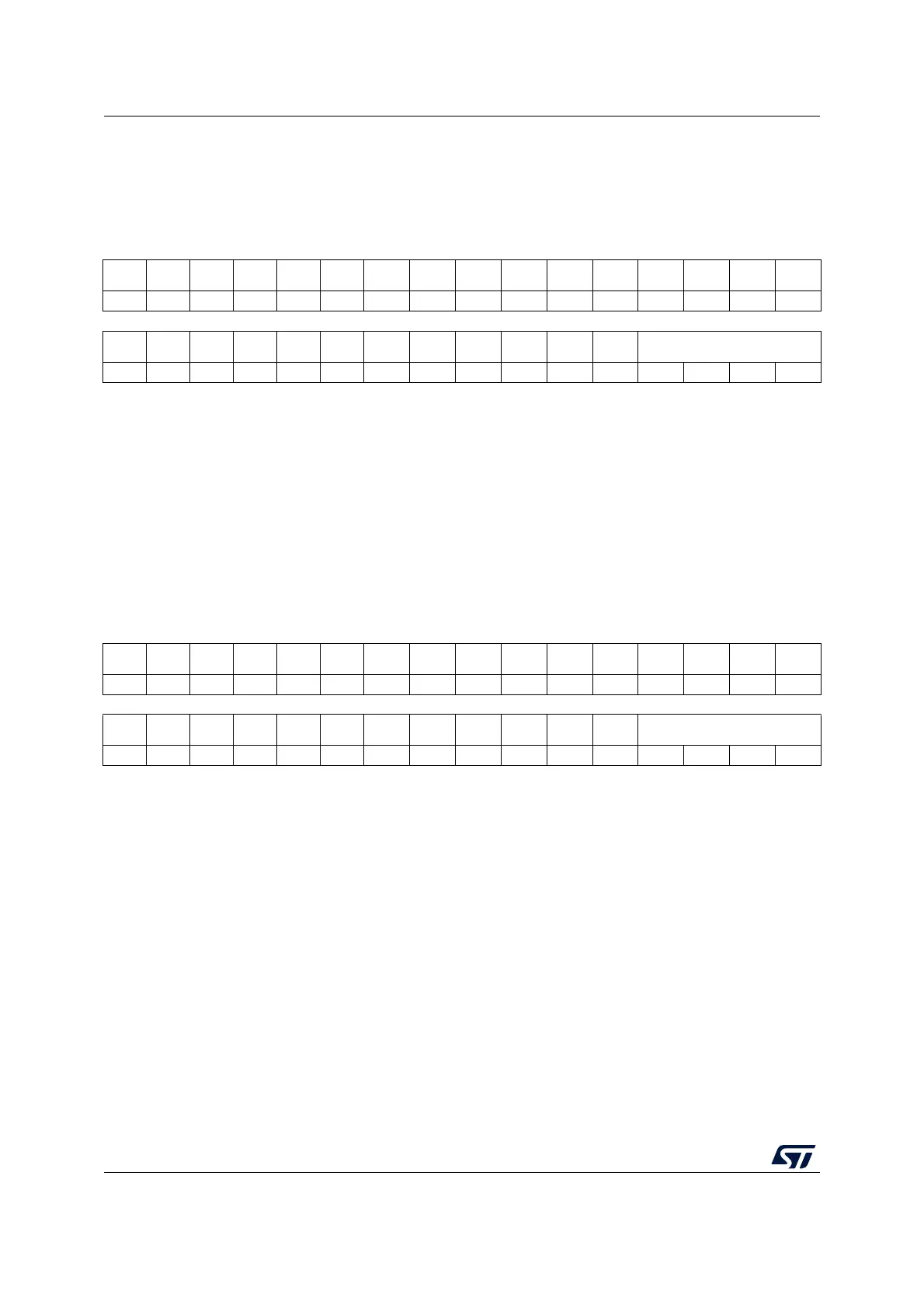

CTI channel gate register (CTI_GATER)

Address offset: 0x140

Reset value: 0x0000 000F

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16

Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res.

1514131211109876543210

Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. CHOUTSTATUS[3:0]

rrrr

Bits 31:4 Reserved, must be kept at reset value.

Bits 3:0 CHOUTSTATUS[3:0]: channel output status

There is one bit of the register for each channel output. When a bit is set to 1, it indicates that

the corresponding channel output is active. When it is set to 0, the corresponding channel

output is inactive.

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16

Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res.

1514131211109876543210

Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. GATEEN[3:0]

rw rw rw rw

Bits 31:4 Reserved, must be kept at reset value.

Bits 3:0 GATEEN[3:0]: channel output enable

For each channel, defines whether an event on that channel can propagate over the CTM to

other CTIs.

0000: Channels events do not propagate.

XXX1: Channel 0 events propagate.

XX1X: Channel 1 events propagate.

X1XX: Channel 2 events propagate.

1XXX: Channel 3 events propagate.

Loading...

Loading...