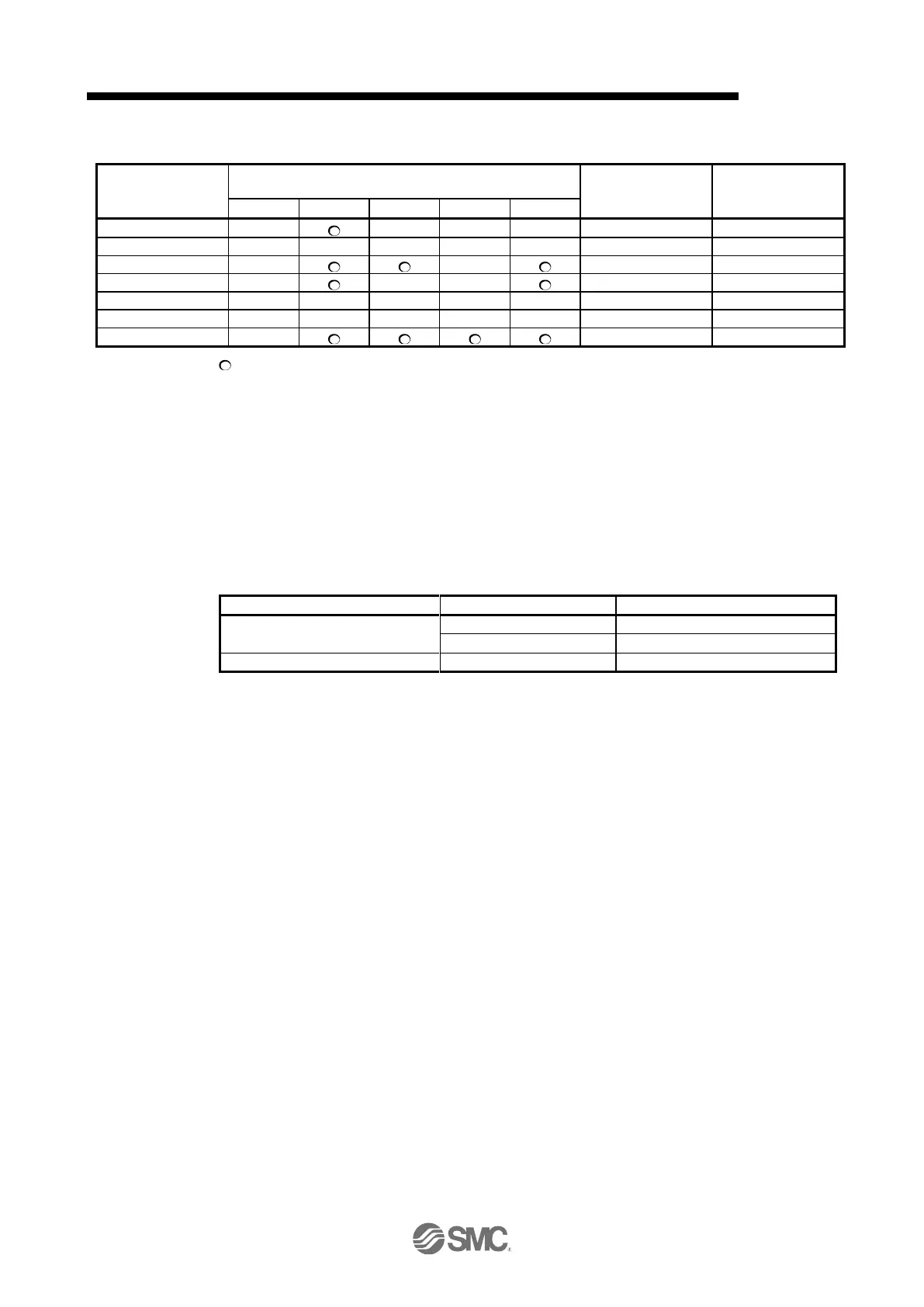

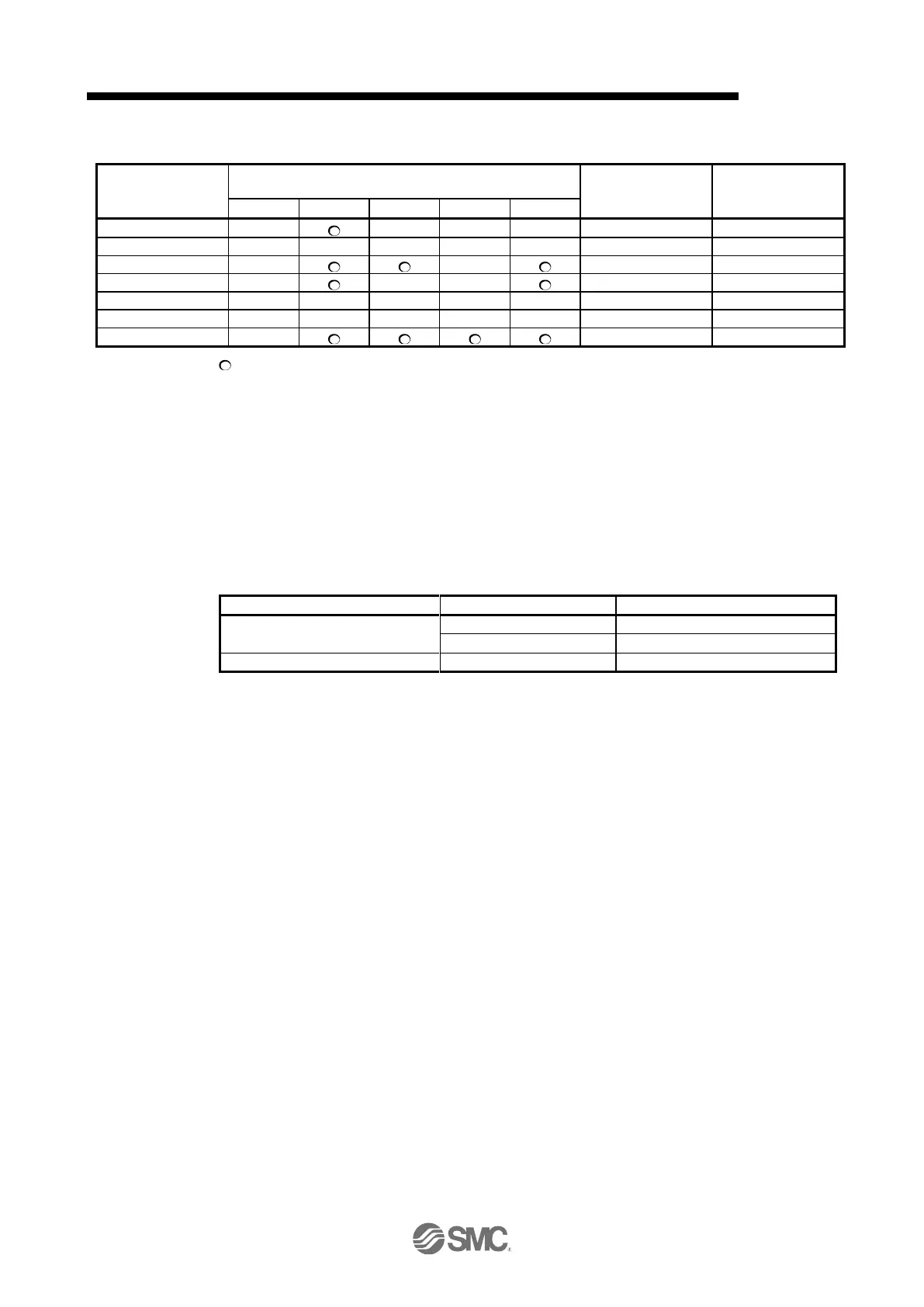

0: OFF 1: ON : ON/OFF

In faulty communication, hold the state of Bit 7 = 1 for as follows for the Fault Reset command to prevent the command from

failing to be recognized.

10 ms ≥ twice the communication cycle: Hold the state for 10 ms.

10 ms < twice the communication cycle: Hold the state for the time determined by doubling the

communication cycle.

Figure 5.1 and Table 5.1 show the transition conditions. The transition from the Switch on Inhibited state to

the Operation state requires Off, On, and Enable operation to be issued in this order. However, with the _

driver, transition to the target state skipping the states in between is possible.

Loading...

Loading...