MPC5553/MPC5554 Microcontroller Reference Manual, Rev. 5

25-32 Freescale Semiconductor

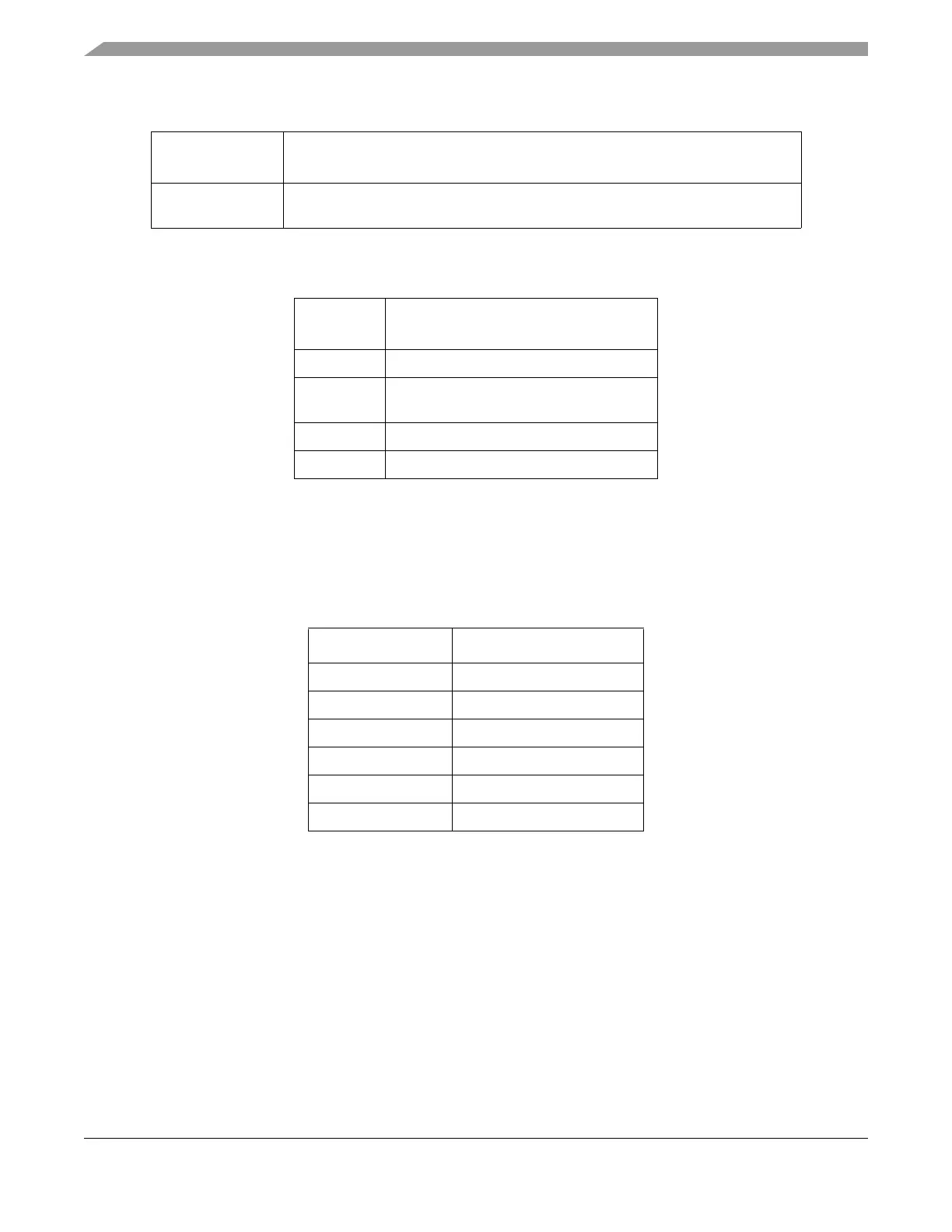

Table 25-22 shows the event code encodings used for certain messages.

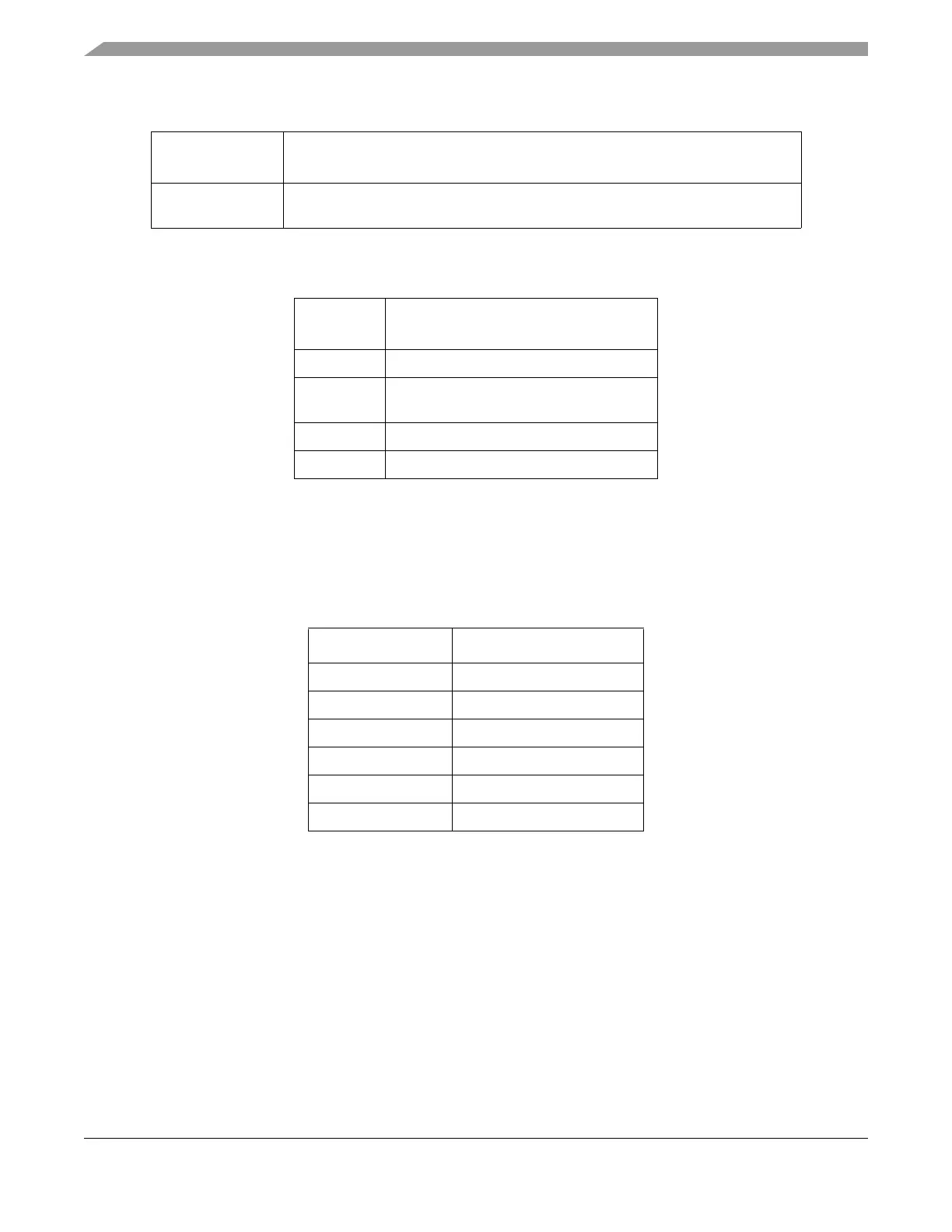

Table 25-23 shows the data trace size encodings used for certain messages.

25.11 NZ6C3 Memory Map/Register Definition

This section describes the NZ6C3 programmer’s model. NZ6C3 registers are accessed using the

JTAG/OnCE port in compliance with IEEE 1149.1. See Section 25.11.10, “ NZ6C3 Register Access

via JTAG / OnCE” for details on NZ6C3 register access.

NOTE

NZ6C3 registers and output signals are numbered using bit 0 as the least

significant bit. This bit ordering is consistent with the ordering defined by

the IEEE-ISTO 5001 standard.

Table 25-24 details the register map for the NZ6C3 module.

Table 25-21. RCODE values (TCODE = 27)

Resource Code

(RCODE)

Description

0001 Program trace, branch / predicate instruction history. This type of packet is

terminated by a stop bit set to 1 after the last history bit.

Table 25-22. Event Code Encoding (TCODE = 33)

Event Code

(EVCODE)

Description

0000 Entry into debug mode

0001 Entry into low power mode (CPU only)

1

1

The device enters Low Power Mode when the Nexus stall

mode is enabled (NZ6C3_DC1[OVC]=0b011) and a

trace message is in danger of over-flowing the Nexus

queue.

0100 Disabling Program Trace

0101–1111 Reserved for future functionality

Table 25-23. Data Trace Size Encodings (TCODE = 5, 6, 13, 14)

DTM Size Encoding Transfer Size

000 Byte

001 Half-word (2 bytes)

010 Word (4 bytes)

011 Double-word (8 bytes)

100 String (3 bytes)

101–111 Reserved

Loading...

Loading...