MPC5553/MPC5554 Microcontroller Reference Manual, Rev. 5

8-12 Freescale Semiconductor

8.2.1.12 RAM ECC Master Number Register (ECSM_REMR)

The REMR is an 8-bit register for capturing the XBAR bus master number of the last, properly-enabled

ECC event in the RAM memory. Depending on the state of the ECSM_ECR, an ECC event in the RAM

causes the address, attributes and data associated with the access to be loaded into the ECSM_REAR,

ECSM_REMR, ECSM_REAT and ECSM_REDRs, and the appropriate flag (RNCE) in the ECSM_ESR

to be asserted.

8.2.1.13 RAM ECC Attributes Register (ECSM_REAT)

The ECSM_REAT is an 8-bit register for capturing the XBAR bus master attributes of the last,

properly-enabled ECC event in the RAM memory. Depending on the state of the ECSM_ECR, an ECC

event in the RAM causes the address, attributes and data associated with the access to be loaded into the

ECSM_REAR, ECSM_REMR, ECSM_REAT and ECSM_REDRs, and the appropriate flag (RNCE) in

the ECSM_ESR to be asserted.

Table 8-11. ECSM_REAR Field Descriptions

Bits Name Description

0–31 REAR

[0:31]

RAM ECC address. Contains the faulting access address of the last, properly-enabled

RAM ECC event. The reset value of this field is undefined.

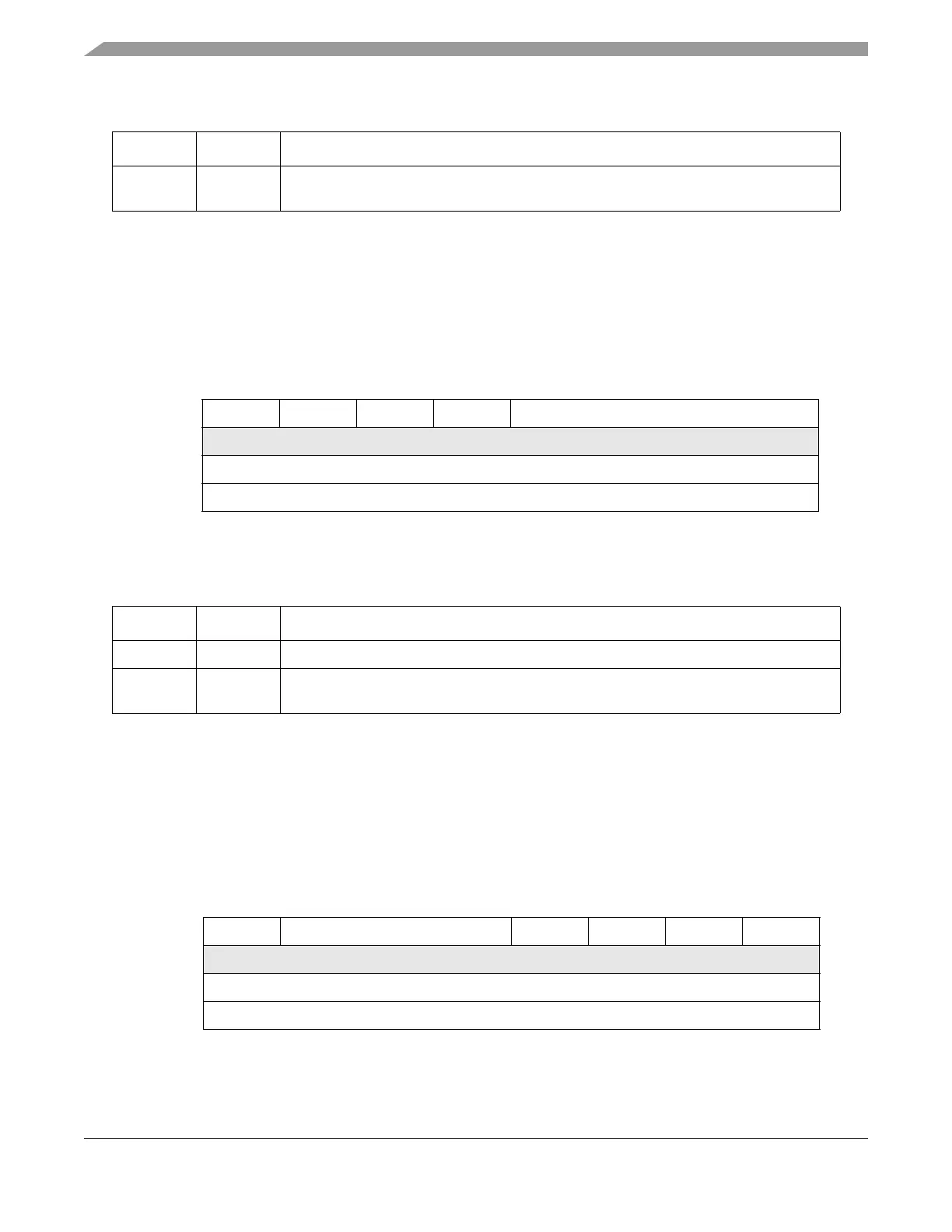

01234567

R0000 REMR

W

Reset00 0 0UUUU

Reg Addr Base + 0x0066

1

“U” signifies a bit that is uninitialized.

Figure 8-10. RAM ECC Master Number Register (ECSM_REMR)

Table 8-12. ECSM_REMR Field Descriptions

Bits Name Description

0–3 — Reserved.

4–7 REMR

[0:3]

RAM ECC master number. Contains the XBAR bus master number of the faulting access

of the last, properly-enabled RAM ECC event. The reset value of this field is undefined.

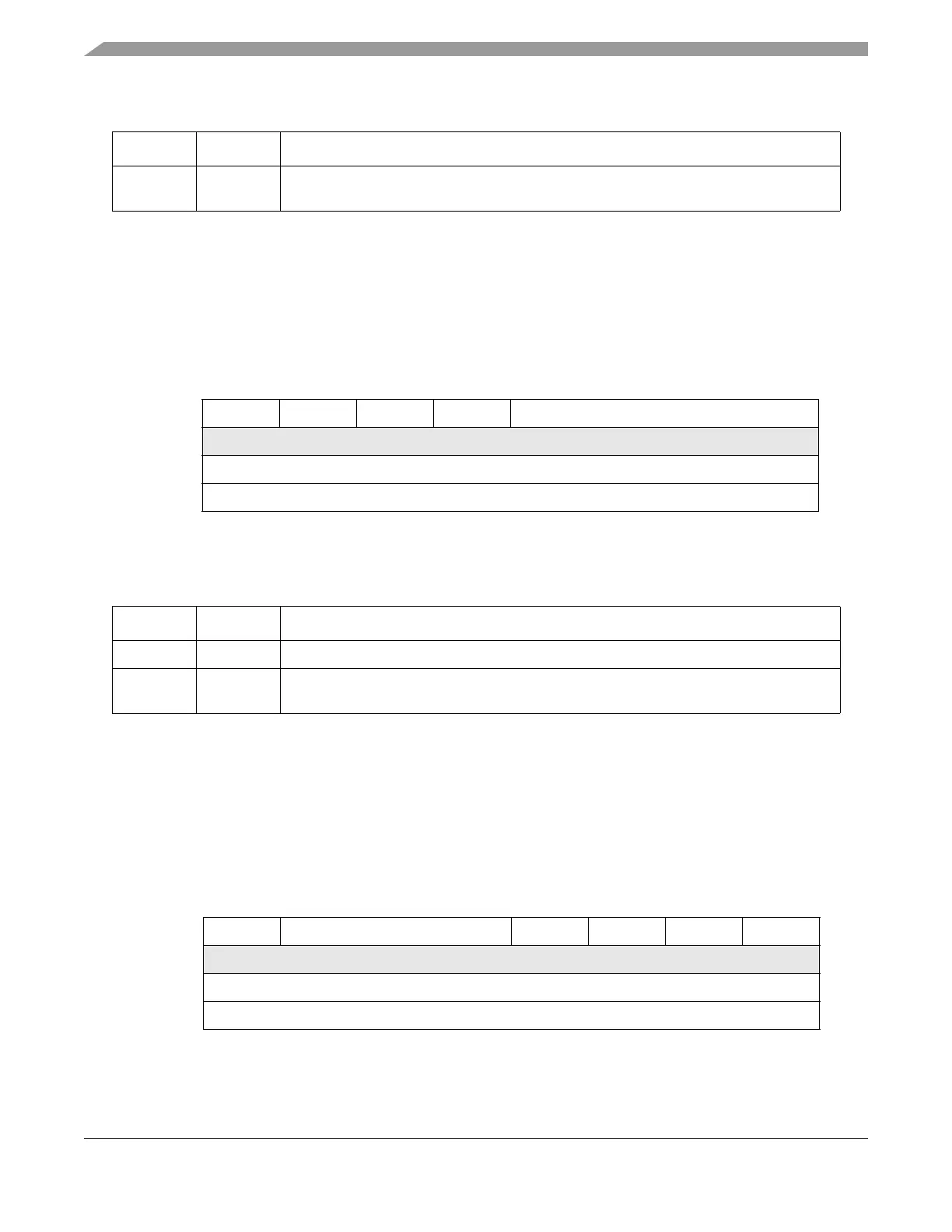

01234567

R WRITE SIZE PROT0 PROT1 PROT2 PROT3

W

Reset UUUUUUUU

Reg Addr Base + 0x0067

1

“U” signifies a bit that is uninitialized.

Figure 8-11. RAM ECC Attributes Register (ECSM_REAT)

Loading...

Loading...