MPC5553/MPC5554 Microcontroller Reference Manual, Rev. 5

Freescale Semiconductor 19-43

19.4 Functional Description

The eQADC provides a parallel interface to two on-chip ADCs, and a single master to single slave serial

interface to an off-chip external device. The two on-chip ADCs are architected to allow access to all the

analog channels.

Initially, command data is contained in system memory in a user defined data queue structure. Command

data is moved between the user-defined queues and CFIFOs by the host CPU or by the eDMA which

responds to interrupt and eDMA requests generated by the eQADC. The eQADC supports software and

hardware triggers from other modules or external pins to initiate transfers of commands from the multiple

CFIFOs to the on-chip ADCs or to the external device.

CFIFOs can be configured to be in single-scan or continuous-scan mode. When a CFIFO is configured to

be in single-scan mode, the eQADC scans the user-defined command queue one time. The eQADC stops

transferring commands from the triggered CFIFO after detecting the EOQ bit set in the last transfer. After

an EOQ bit is detected, software involvement is required to rearm the CFIFO so that it can detect new

trigger events.

When a CFIFO is configured for continuous-scan mode, the whole user command queue is scanned

multiple times. After the detection of an asserted EOQ bit in the last command transfer, command transfers

can continue or not depending on the mode of operation of the CFIFO.

The eQADC can also in parallel and independently of the CFIFOs receive data from the on-chip ADCs or

from off-chip external device into multiple RFIFOs. Result data is moved from the RFIFOs to the

user-defined result queues in system memory by the host CPU or by the eDMA.

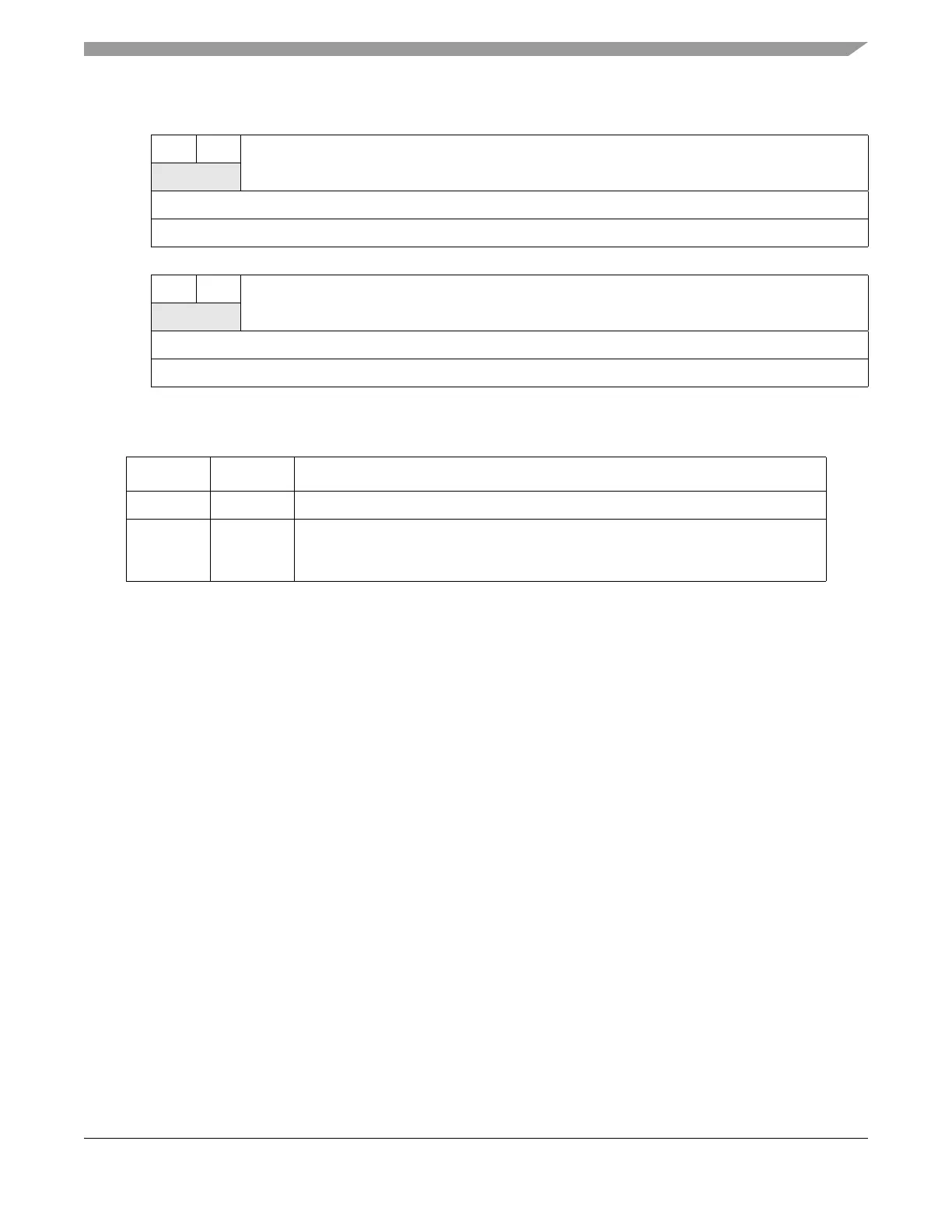

0123456789101112131415

R0 0 OCC0

W

Reset0000000000000000

Reg Addr 0x05

0123456789101112131415

R0 0 OCC1

W

Reset0000000000000000

Reg Addr 0x05

Figure 19-23. ADCn Offset Calibration Constant Registers (ADCn_OCCR)

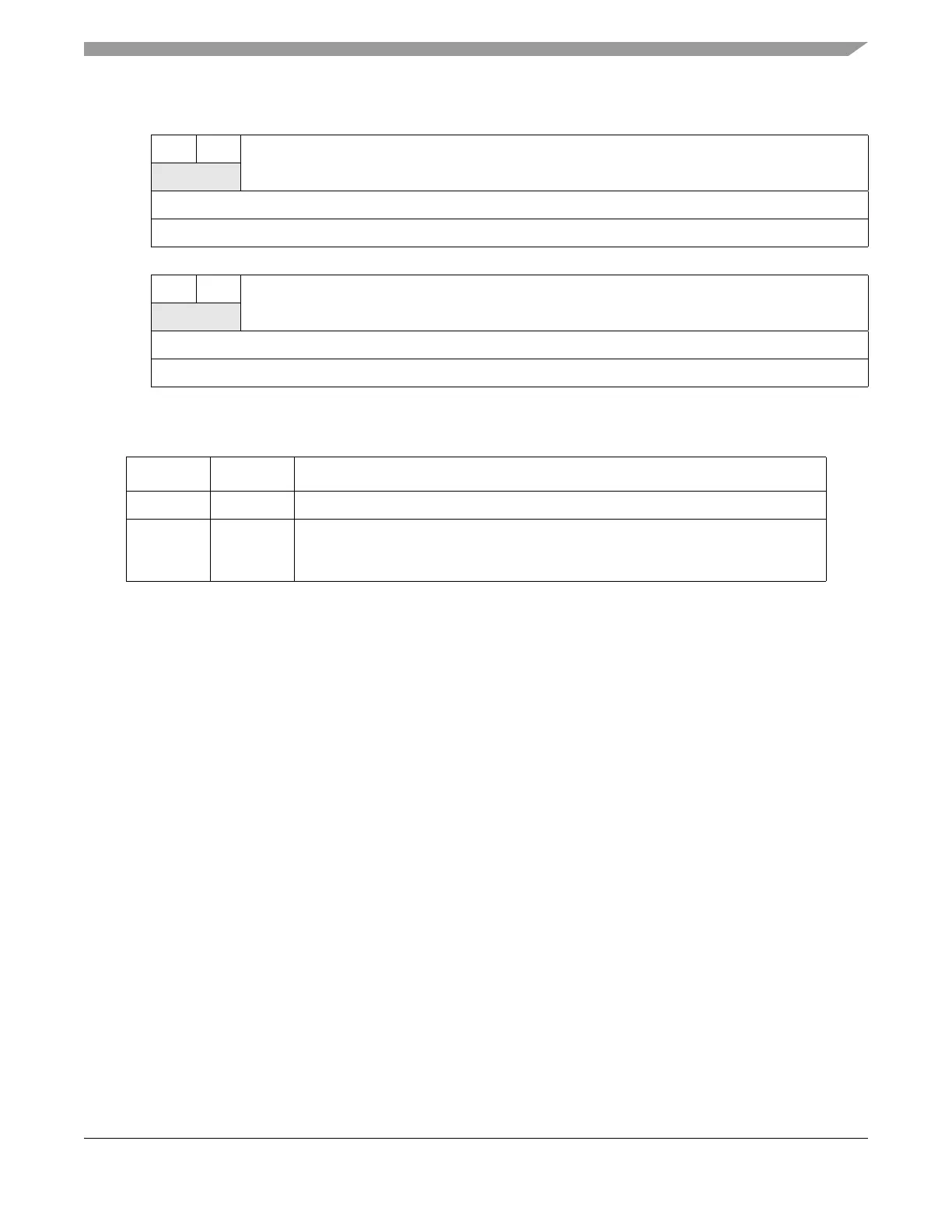

Table 19-33. ADCn_OCCR Field Descriptions

Bits Name Description

0–1 — Reserved.

2–15 OCCn

[0:13]

ADCn offset calibration constant. Contains the offset calibration constant used to

fine-tune ADCn conversion results. Negative values should be expressed using the

two’s complement representation.

Loading...

Loading...