MPC5553/MPC5554 Microcontroller Reference Manual, Rev. 5

Freescale Semiconductor 17-67

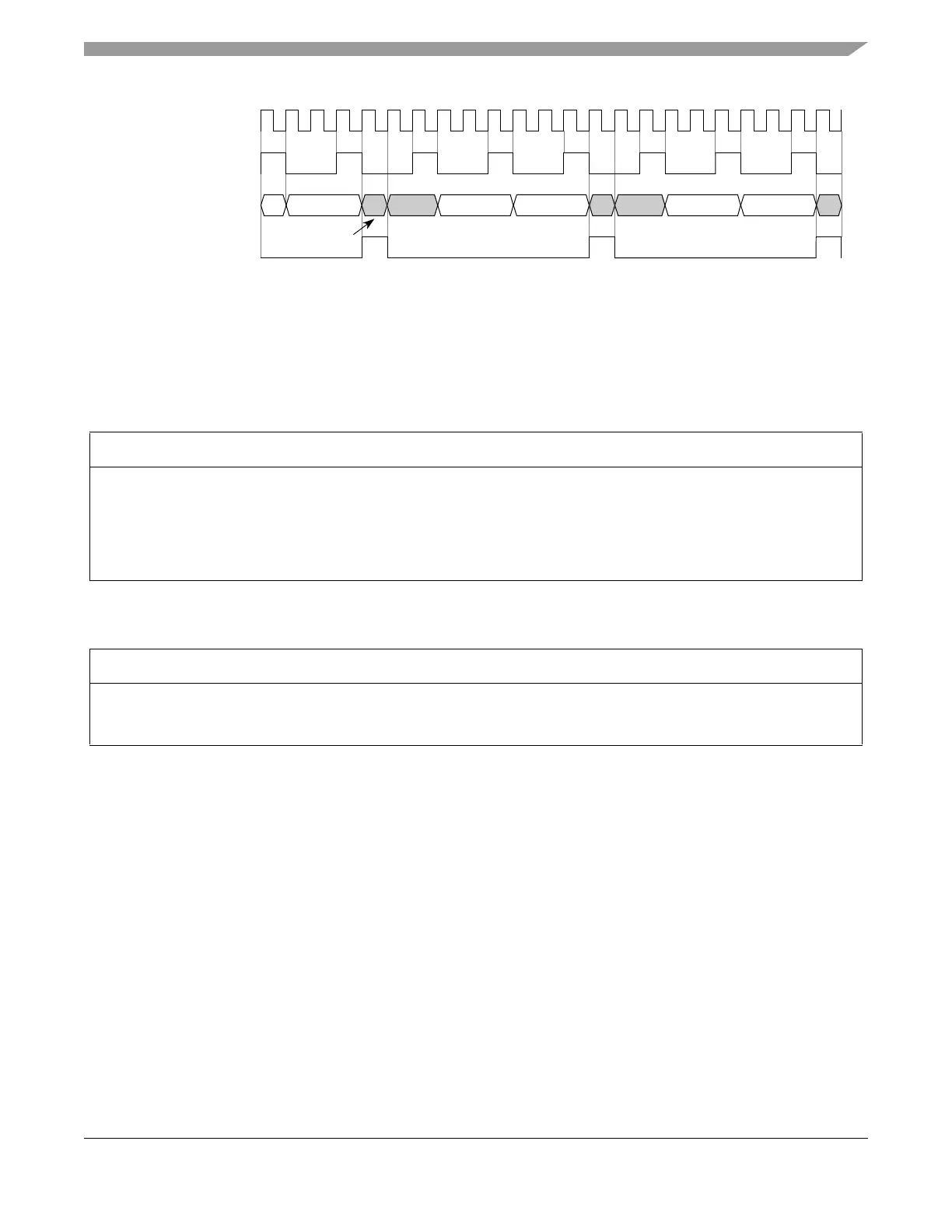

Figure 17-57. eMIOS Time Base Example — Prescale Ratio = 2, Match Value = 5

17.6 Revision History

Table 17-32. Changes to MPC5553/5554 RM for Rev. 4.0 Release

Description of Change

• Added Table 17-14 Mode of Operation: GPIO Mode to the section titled General Purpose Input/Output Mode.

• Added Table 17-23 “Mode of Operation: MC Mode” to Modulus Counter Mode (MC) section.

• Added Table 17-24 “Mode of Operation: OPWFM Mode” to Output Pulse Width Frequency Modulation (OPWFM) section.

• Added these Mode of Operation tables for all modes.

• Added this first sentence to the OPWFM mode:

"In this mode, the duty cycle is (register A1 + 1) and the period is (register B1 + 1)."

Table 17-33. Changes to MPC5553/5554 RM for Rev. 5.0 Release

Description of Change

• Corrected the direction of arrows in the figure “Unified Channel Block Diagram”.

• In the table “EMIOS_CCRn Field Description”, DMA bit description, added the sentence “eMIOS channel 6, 7,10, 11, 16,

17, 18, and 19 DMA support is only for MPC5554.”

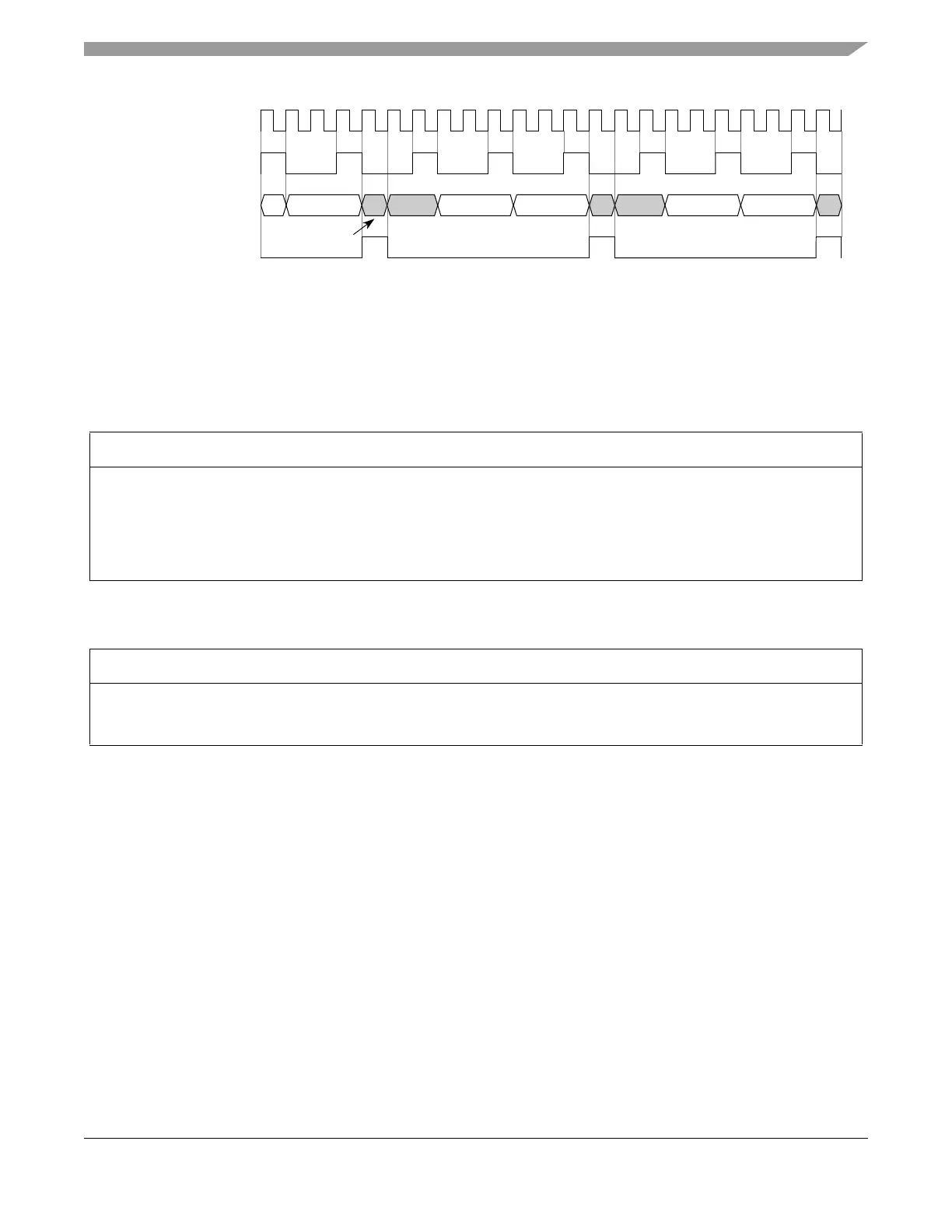

Prescaled Clock

1 2 0 3

NOTE: The period of the time base does not include the match value. When a match occurs,

the first clock cycle is used to clear the internal counter, starting another period

Clock

See Note

3 1 2 3 0 1 2

(Ratio = 3)

Match Value = 3

Internal Counter

EMIOS_CCNTRn

Loading...

Loading...