MPC5553/MPC5554 Microcontroller Reference Manual, Rev. 5

25-10 Freescale Semiconductor

25.4 NDI Functional Description

25.4.1 Enabling Nexus Clients for TAP Access

After the NDI is out of the reset state, the loading of a specific instruction in the JTAG controller (JTAGC)

block is required to grant the NDI ownership of the TAP. Each Nexus client has its own JTAGC instruction

opcode for ownership of the TAP, granting that client the means to read/write its registers. The JTAGC

instruction opcode for each Nexus client is shown in Table 25-4. After the JTAGC opcode for a client has

been loaded, the client is enabled by loading its NEXUS-ENABLE instruction. The NEXUS-ENABLE

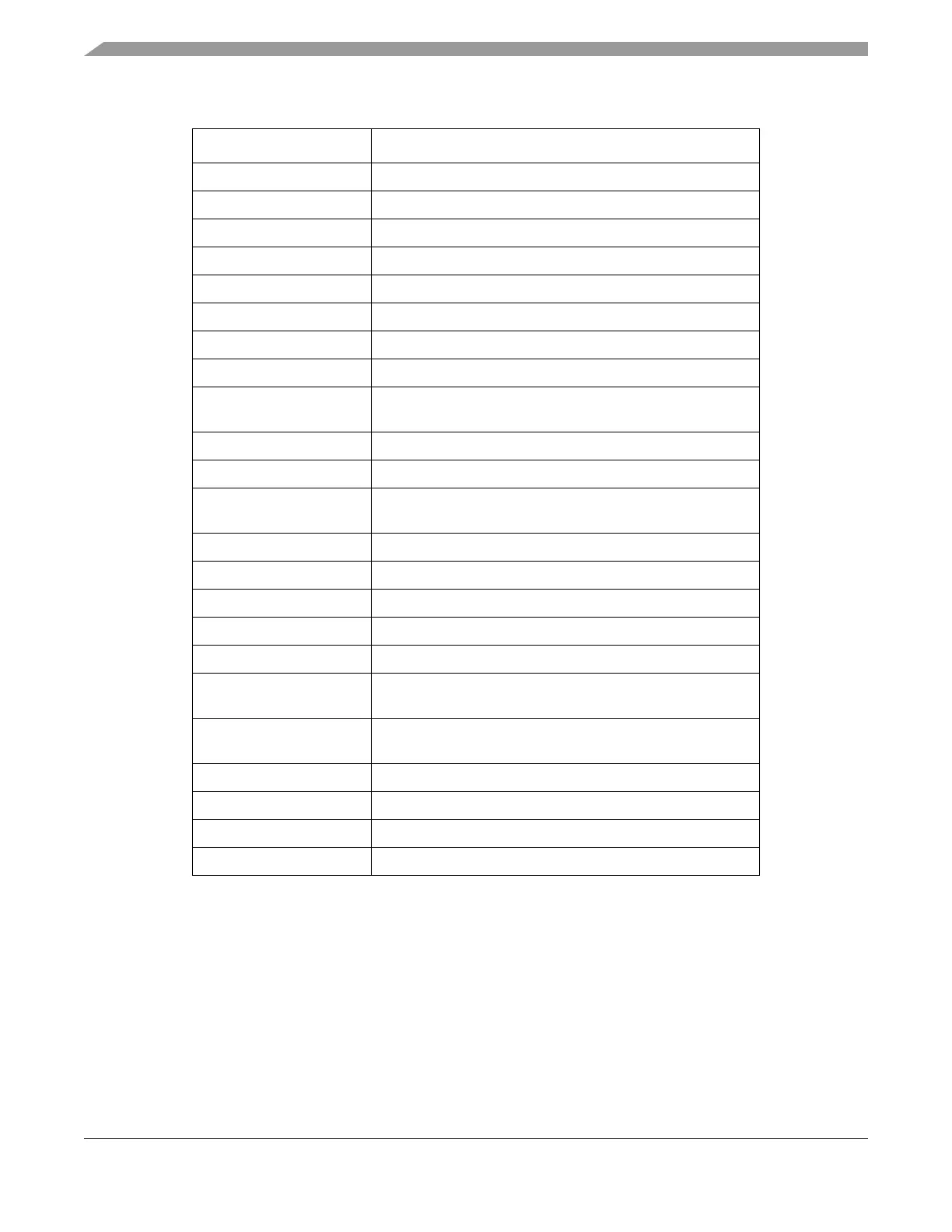

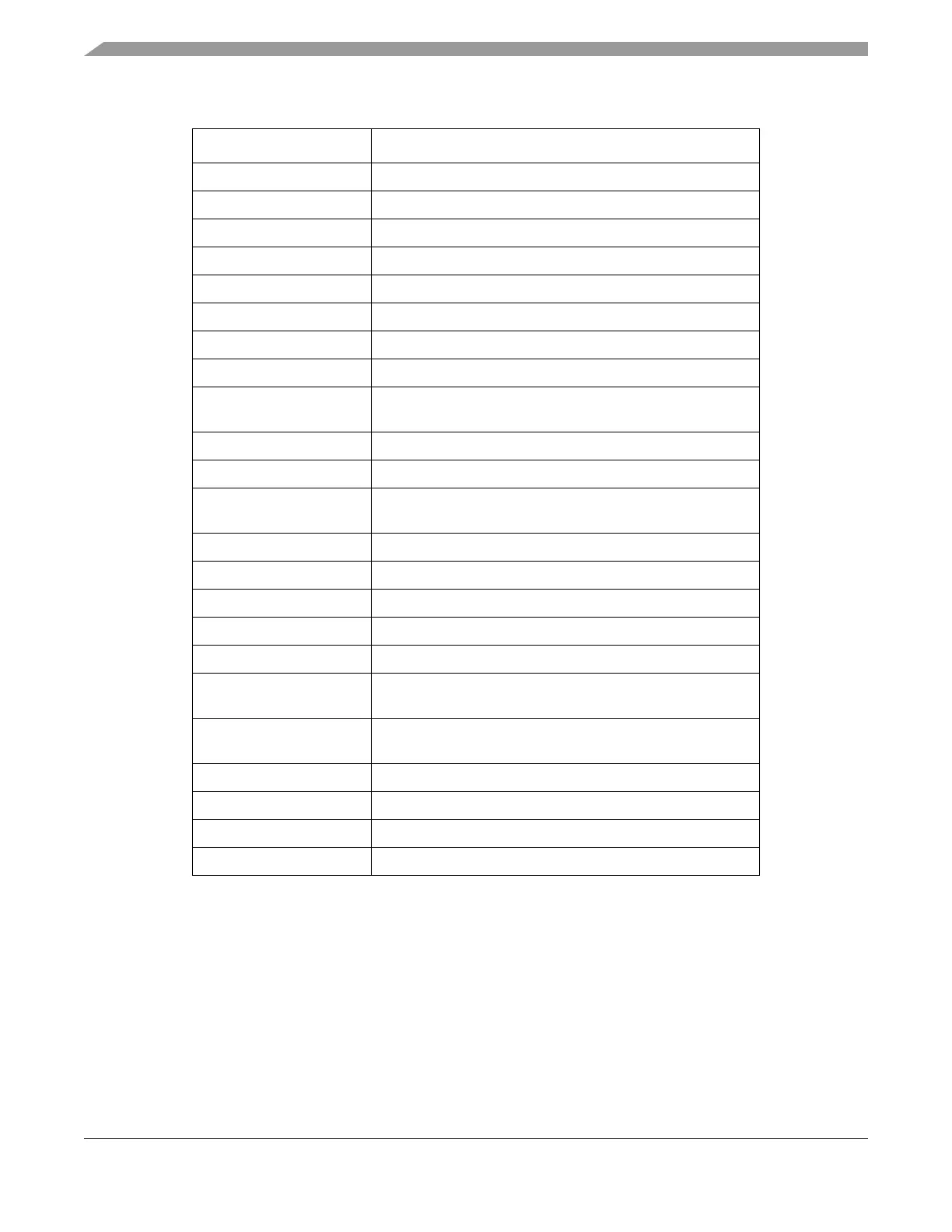

010 0000 Instruction Address Compare 1 (IAC1)

010 0001 Instruction Address Compare 2 (IAC2)

010 0010 Instruction Address Compare 3 (IAC3)

010 0011 Instruction Address Compare 4 (IAC4)

010 0100 Data Address Compare 1 (DAC1)

010 0101 Data Address Compare 2 (DAC2)

010 0110 Reserved

010 0111 Reserved

010 1000 -

010 1011

Reserved

010 1100 Debug Counter Register (DBCNT)

010 1101 Debug PCFIFO (PCFIFO) (read-only)

010 1110 -

010 1111

Reserved

011 0000 Debug Status Register (DBSR)

011 0001 Debug Control Register 0 (DBCR0)

011 0010 Debug Control Register 1 (DBCR1)

011 0011 Debug Control Register 2 (DBCR2)

011 0100 Debug Control Register 3 (DBCR3)

011 0101 -

101 1111

Reserved (do not access)

111 0000 -

111 1011

General Purpose Register Selects [0:11]

111 1100 Nexus3-Access

111 1101 LSRL Select

111 1110 Enable_OnCE (and Bypass)

111 1111 Bypass

Table 25-3. OnCE Register Addressing (Continued)

OCMD, RS[0:6] Register Selected

Loading...

Loading...