MPC5553/MPC5554 Microcontroller Reference Manual, Rev. 5

Freescale Semiconductor 5-11

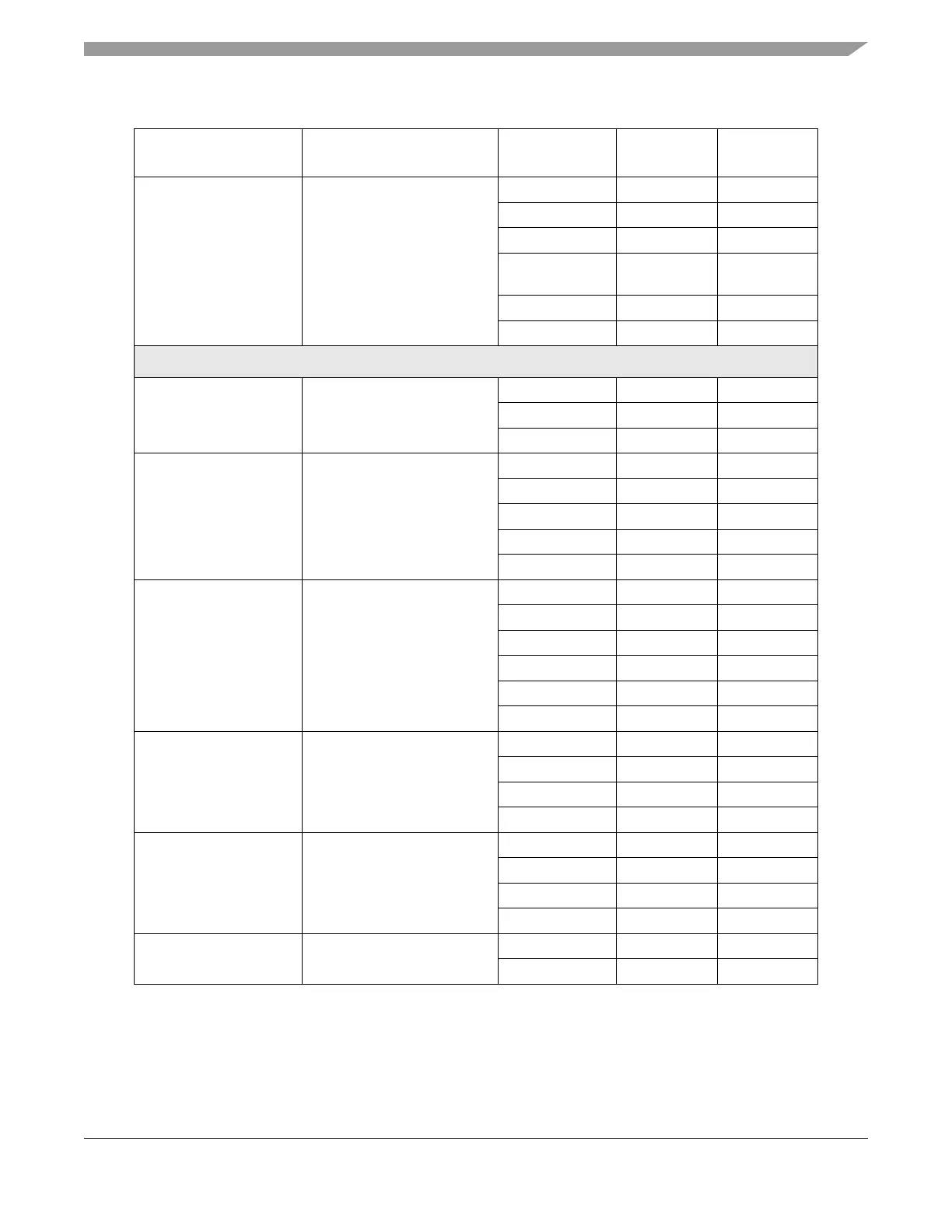

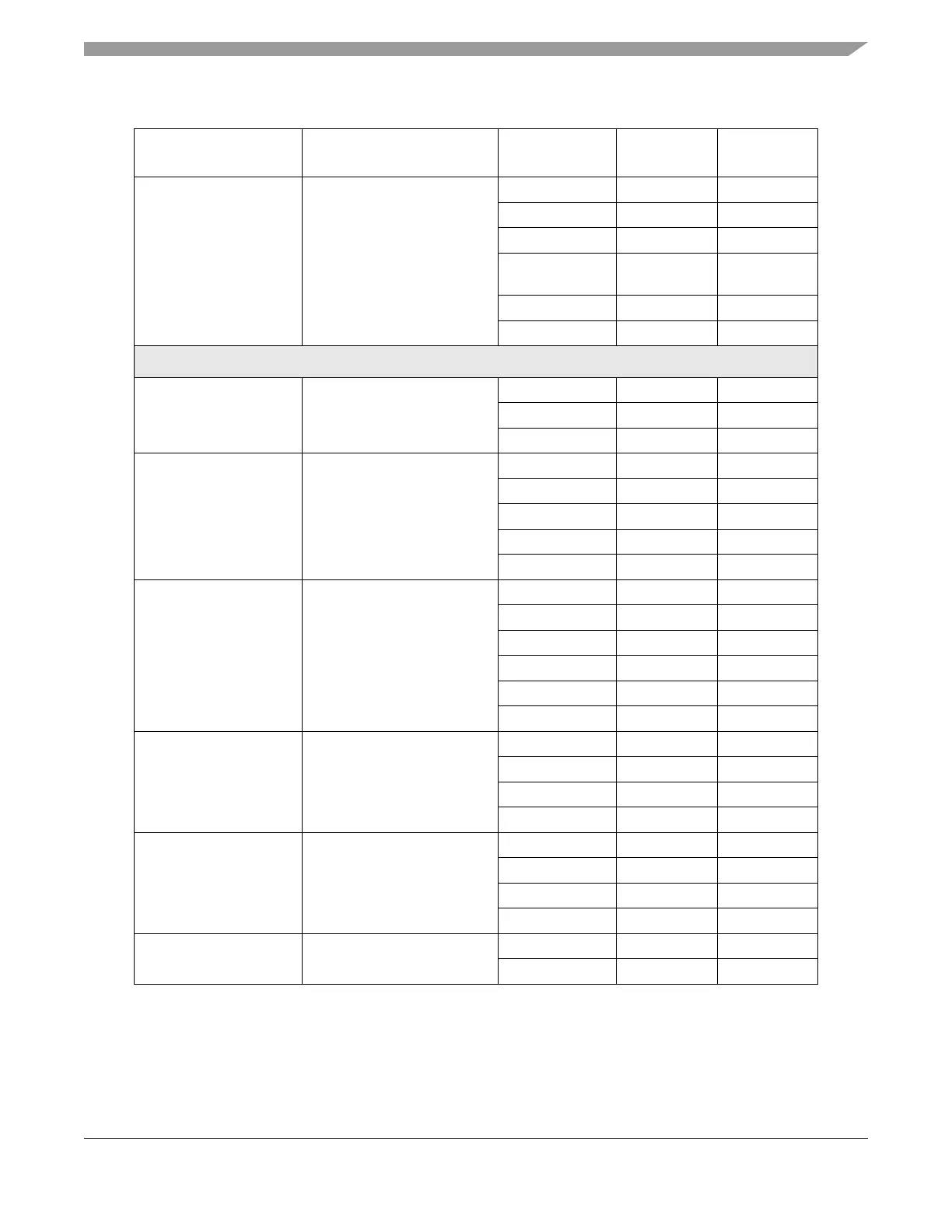

PBRIDGE_A_OPACR2 PBRIDGE_A_Base + 0x048 0 eTPU 0b0100

1 — 0b0100

2 eTPU PRAM 0b0100

3 eTPU PRAM

Mirror

0b0100

4 eTPU SCM 0b0100

5-7 — 0b0100

PBRIDGE_B

PBRIDGE_B_PACR0 PBRIDGE_B_Base + 0x020 0 PBRIDGE_B 0b0101

1 XBAR 0b0100

2-7 — 0b0000

PBRIDGE_B_PACR2 PBRIDGE_B_Base + 0x028 0 ESCM 0b0100

1 eDMA 0b0100

2 INTC 0b0100

3

1

FEC

1

0b0100

4-7 — 0b0000

PBRIDGE_B_OPACR0 PBRIDGE_B_Base + 0x040 0 eQADC 0b0100

1-3 — 0b0100

4

2

DSPI_A

2

0b0100

5 DSPI_B 0b0100

6 DSPI_C 0b0100

7 DSPI_D 0b0100

PBRIDGE_B_OPACR1 PBRIDGE_B_Base + 0x044 0-3 — 0b0100

4 eSCI_A 0b0100

5 eSCI_B 0b0100

6-7 — 0b0100

PBRIDGE_B_OPACR2 PBRIDGE_B_Base + 0x048 0 FlexCAN_A 0b0100

1

2

FlexCAN_B

2

0b0100

2 FlexCAN_C 0b0100

3-7 — 0b0100

PBRIDGE_B_OPACR3 PBRIDGE_B_Base + 0x04C 0-6 — 0b0100

7 BAM 0b0100

1

In MPC5553 only, not present in MPC5554

2

In MPC5554 only, not present in MPC5553

Table 5-6. PACR/OPACR Access Control Registers and Peripheral Mapping (Continued)

Register Register Address

Peripheral

Access Field #

Peripheral

Type

Access Field

Default Value

Loading...

Loading...