MPC5553/MPC5554 Microcontroller Reference Manual, Rev. 5

8-4 Freescale Semiconductor

8.2.1.3 ECC Configuration Register (ECSM_ECR)

The ECSM_ECR is an 8-bit control register for specifying whether memory errors are reported during

RAM or flash accesses. The occurrence of a non-correctable error causes the current access to be

terminated with an error condition. In many cases, this error termination is reported directly by the

initiating bus master. The ECC reporting logic in the ECSM provides an optional error interrupt

mechanism to signal non-correctable memory errors. In addition to the interrupt generation, the ECSM

captures specific information (memory address, attributes and data, bus master number, etc.) which may

be useful for subsequent failure analysis.

8.2.1.4 ECC Status Register (ECSM_ESR)

The ECSM_ESR is an 8-bit control register for signaling which types of properly-enabled ECC events

have been detected. The ESR signals the last, properly-enabled memory event to be detected. The

generation of the ECSM ECC interrupt request is defined by the boolean equation:

ECSM_ECC_IRQ

= ECSM_ECR[ERNCR] & ECSM_ESR[RNCE] // ram, noncorrectable error

| ECSM_ECR[EFNCR] & ECSM_ESR[FNCE] // Flash, noncorrectable error

where the combination of a properly-enabled category in the ECSM_ECR and the detection of the

corresponding condition in the ECSM_ESR produces the interrupt request.

The ECSM allows a maximum of one bit of the ECSM_ESR to be asserted at any given time. This

preserves the association between the ECSM_ESR and the corresponding address and attribute registers,

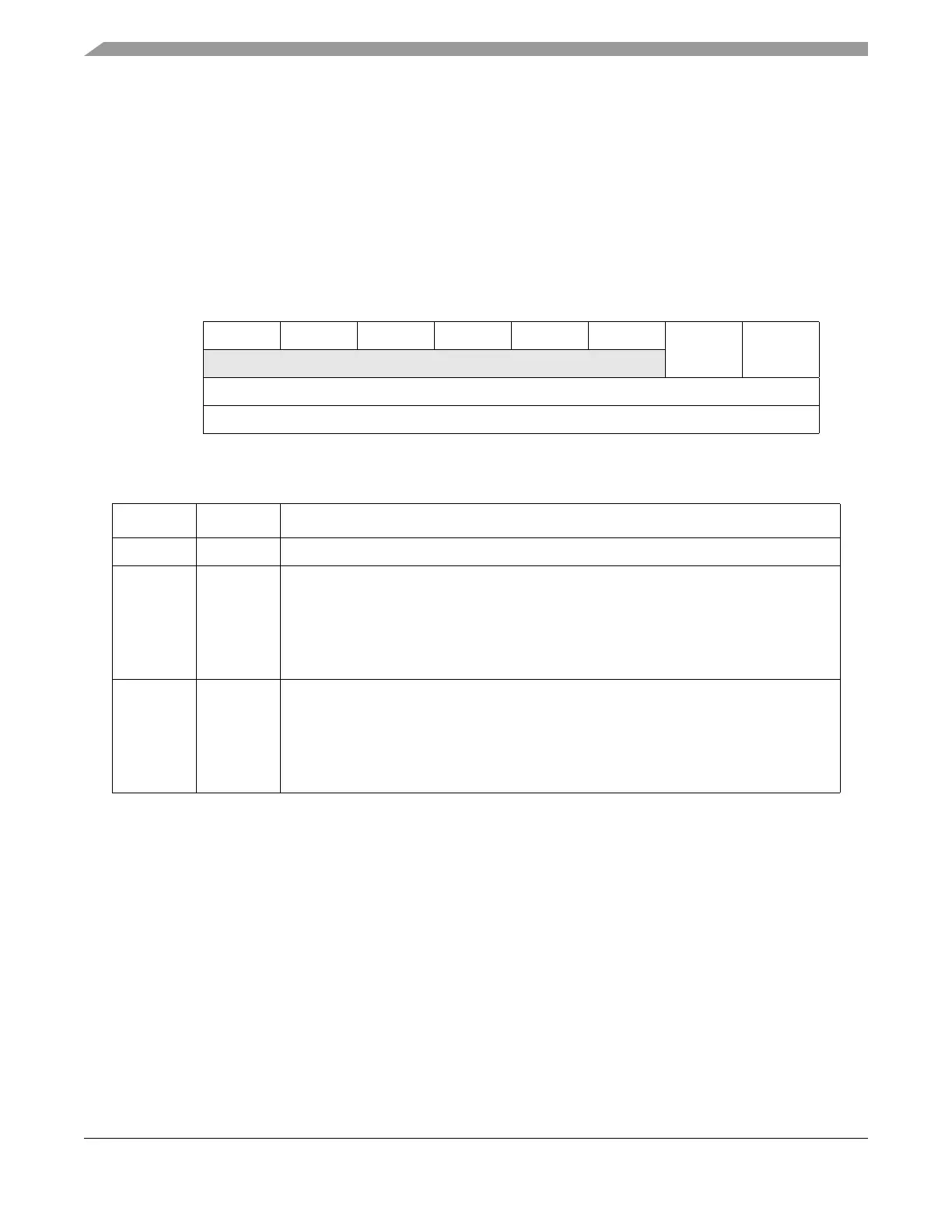

01234567

R000000ERNCREFNCR

W

Reset00000000

Reg Addr Base (0xFFF4_0000) + 0x0043

Figure 8-1. ECC Configuration Register (ECSM_ECR)

Table 8-3. ECSM_ECR Field Definitions

Bits Name Description

0–5 — Reserved.

6 ERNCR Enable RAM non-correctable reporting. The occurrence of a non-correctable multi-bit RAM

error generates a ECSM ECC interrupt request as signalled by the assertion of

ECSM_ESR[RNCE]. The faulting address, attributes and data are also captured in the

REAR, REMR, REAT and REDR registers.

0 Reporting of non-correctable RAM errors is disabled.

1 Reporting of non-correctable RAM errors is enabled.

7 EFNCR Enable flash non-correctable reporting. The occurrence of a non-correctable multi-bit flash

error generates a ECSM ECC interrupt request as signalled by the assertion of

ECSM_ESR[FNCE]. The faulting address, attributes and data are also captured in the

FEAR, FEMR, FEAT and FEDR registers.

0 Reporting of non-correctable flash errors is disabled.

1 Reporting of non-correctable flash errors is enabled.

Loading...

Loading...