MPC5553/MPC5554 Microcontroller Reference Manual, Rev. 5

Freescale Semiconductor 19-13

19.3.2 eQADC Register Descriptions

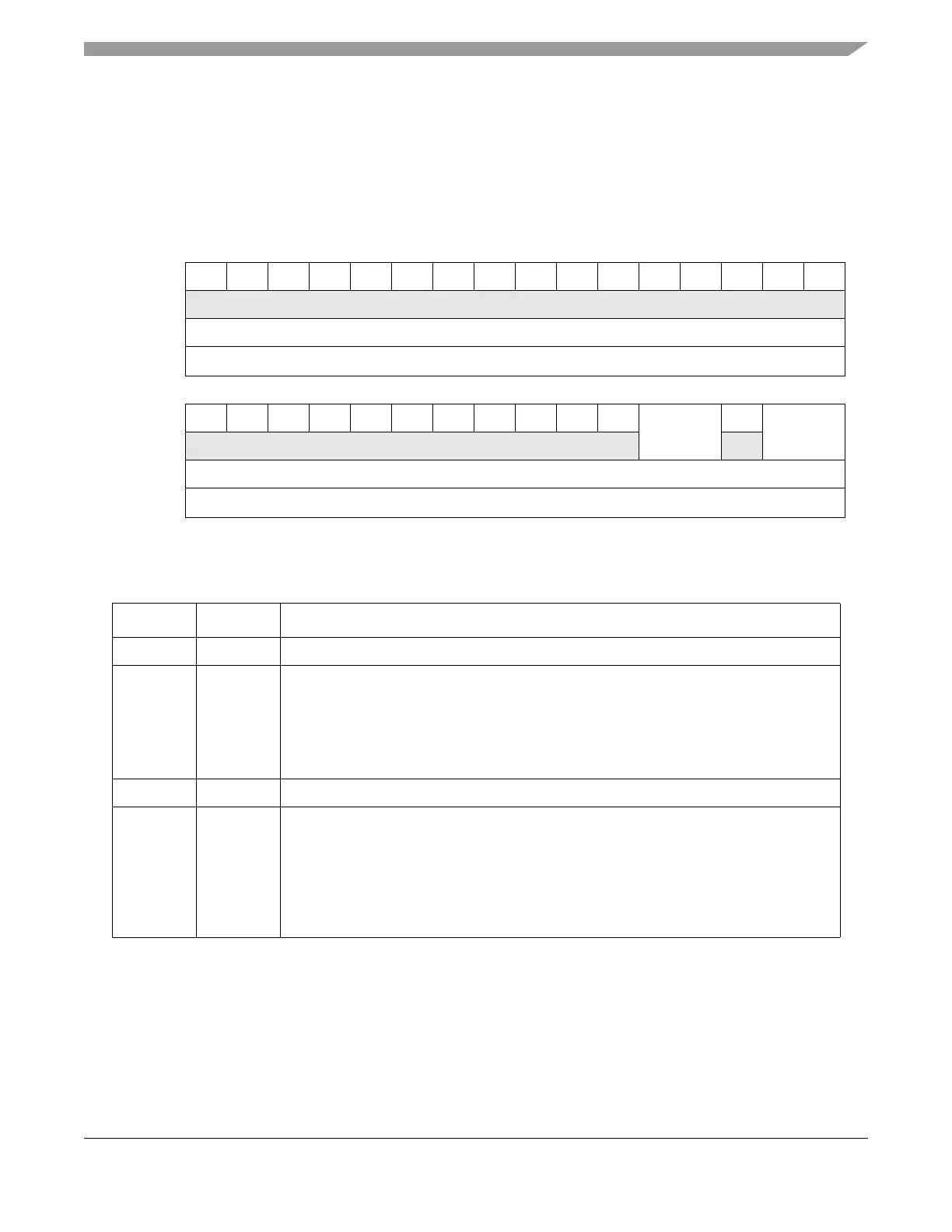

19.3.2.1 eQADC Module Configuration Register (EQADC_MCR)

The EQADC_MCR contains bits used to control how the eQADC responds to a debug mode entry request,

and to enable the eQADC SSI interface.

NOTE

Disabling the eQADC SSI (0b00 write to ESSIE) or serial transmissions

from the eQADC SSI (0b10 write to ESSIE) while a serial transmission is

in progress results in the abort of that transmission.

0123456789101112131415

R0000000000000000

W

Reset0000000000000000

Reg Addr

Base+ 0x0000

16 17 18 19 20 21 22 23 24 25 26 27 28 29 30 31

R00000000000 ESSIE 0 DBG

W

Reset0000000000000000

Reg Addr

Base+ 0x0000

Figure 19-2. eQADC Module Configuration Register (EQADC_MCR)

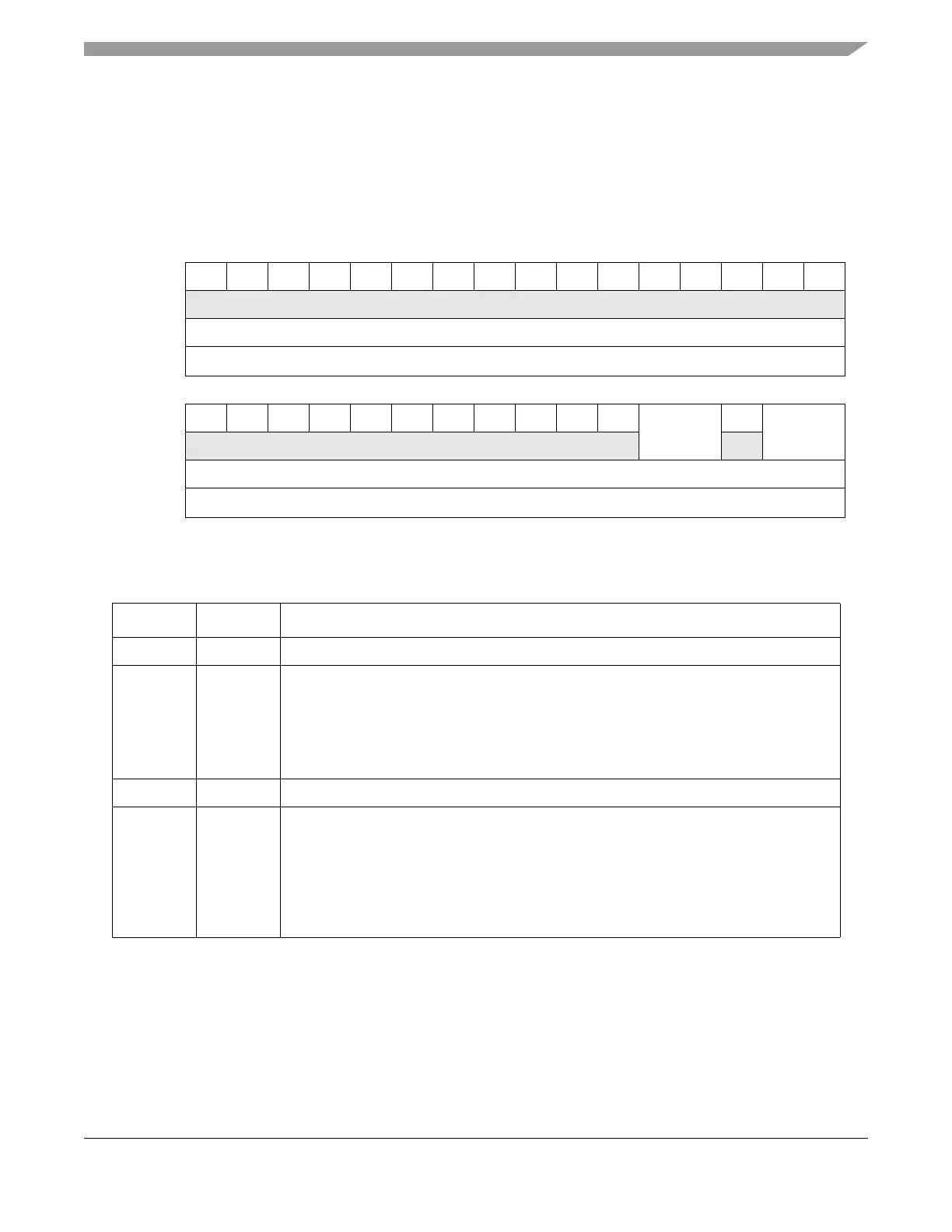

Table 19-3. EQADC_MCR Field Descriptions

Bits Name Description

0–26 — Reserved.

27–28 ESSIE

[0:1]

eQADC synchronous serial interface enable. Defines the eQADC synchronous serial

interface operation.

00 eQADC SSI is disabled

01 Reserved

10 eQADC SSI is enabled, FCK is free running, and serial transmissions are disabled

11 eQADC SSI is enabled, FCK is free running, and serial transmissions are enabled

29 — Reserved.

30–31 DBG

[0:1]

Debug enable. Defines the eQADC response to a debug mode entry request.

00 Do not enter debug mode

01 Reserved

10 Enter debug mode. If the eQADC SSI is enabled, FCK stops while the eQADC is in

debug mode.

11 Enter debug mode. If the eQADC SSI is enabled, FCK is free running while the eQADC

is in debug mode

Loading...

Loading...