MPC5553/MPC5554 Microcontroller Reference Manual, Rev. 5

20-8 Freescale Semiconductor

20.3.2 Register Descriptions

20.3.2.1 DSPI Module Configuration Register (DSPIx_MCR)

The DSPIx_MCR contains bits which configure various attributes associated with DSPI operation. The

HALT and MDIS bits can be changed at any time but will only take effect on the next frame boundary.

Only the HALT and MDIS bits in the DSPIx_MCR may be changed while the DSPI is running.

Base + 0x00C8 DSPIx_COMPR DSPI DSI transmit comparison register 32

Base + 0x00CC DSPIx_DDR DSPI DSI deserialization data register 32

1

Only available in the MPC5554.

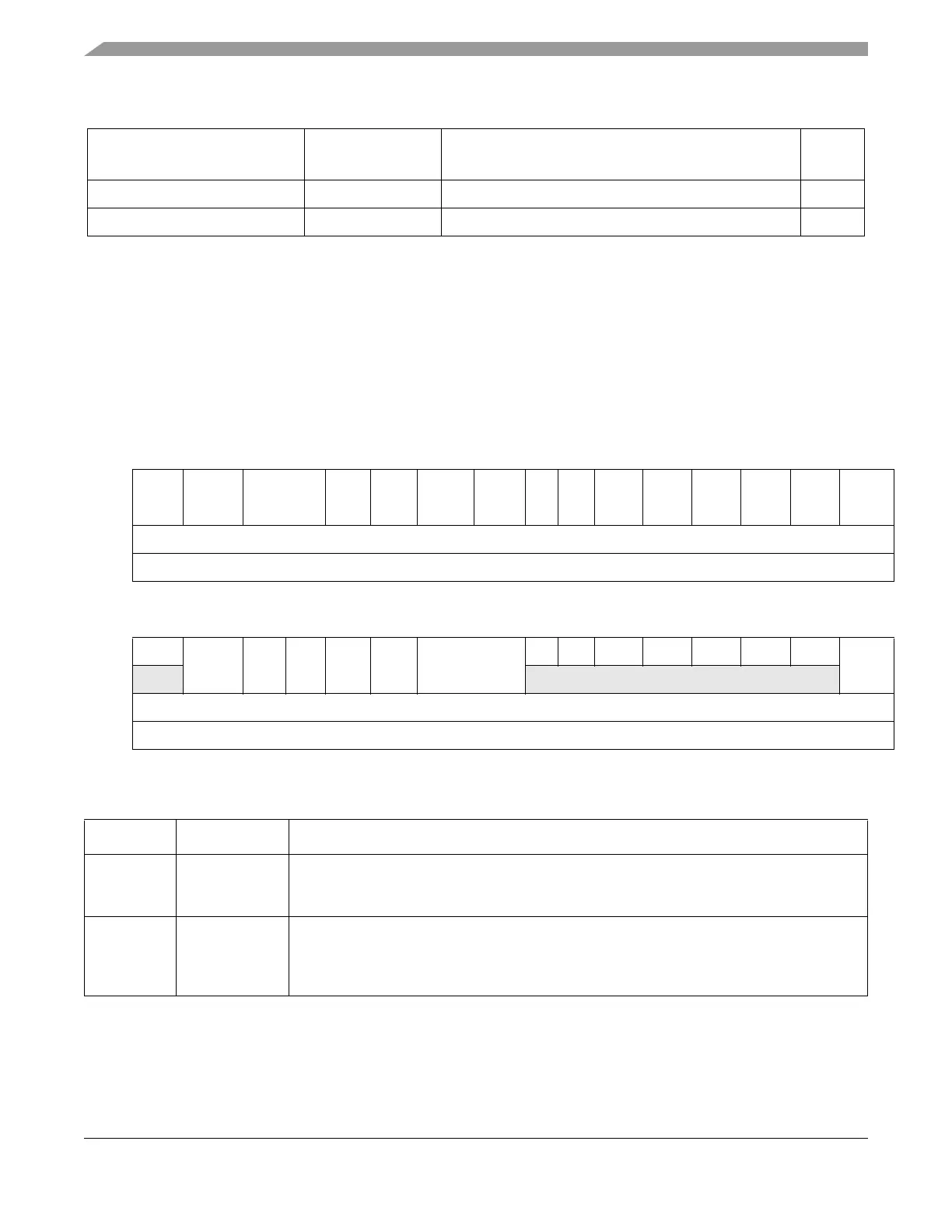

0 1 2 3 4 5 6 7 8 9 10 11 12 13 14 15

RMSTR CONT_

SCKE

DCONF FRZ MTFE PCSSE ROOE 0 0 PCSIS

5

PCSIS

4

PCSIS

3

PCSIS

2

PCSIS

1

PCSIS

0

W

Reset 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0

Reg Addr Base

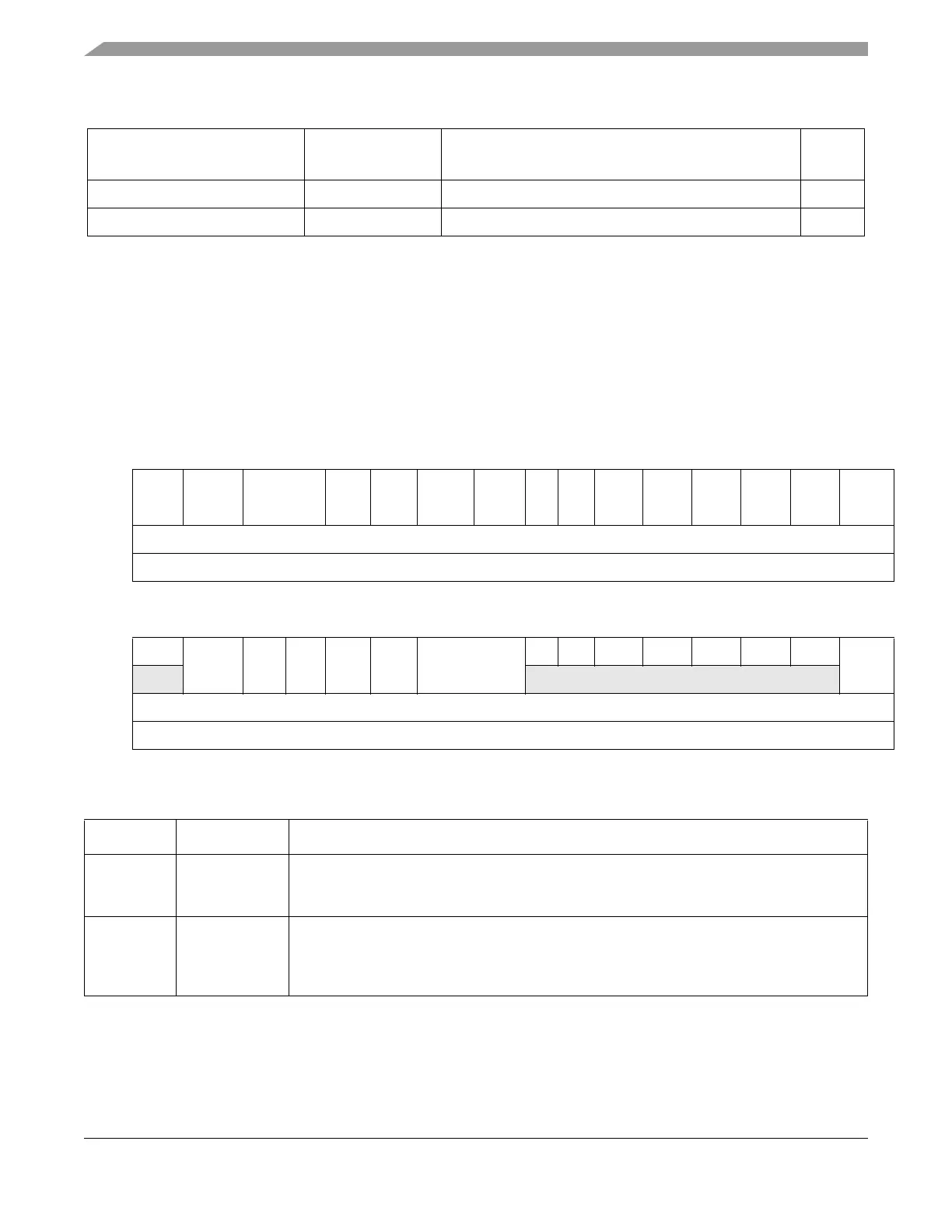

16 17 18 19 20 21 22 23 24 25 26 27 28 29 30 31

R0 MDISDIS_

TXF

DIS_

RXF

CLR_

TXF

CLR_

RXF

SMPL_PT 0 0 0 0 0 0 0 HALT

W

Reset 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 1

Reg Addr Base

Figure 20-3. DSPI Module Configuration Register (DSPIx_MCR)

Table 20-3. DSPIx_MCR Field Descriptions

Bits Name Description

0 MSTR Master/slave mode select. Configures the DSPI for either master mode or slave mode.

0 DSPI is in slave mode

1 DSPI is in master mode

1 CONT_SCKE Continuous SCK enable. Enables the serial communication clock (SCK) to run continuously.

See Section 20.4.8, “Continuous Serial Communications Clock,” for details.

0 Continuous SCK disabled

1 Continuous SCK enabled

Table 20-2. DSPI Detailed Memory Map (Continued)

Address Register Name Register Description

Size

(bits)

Loading...

Loading...