MPC5553/MPC5554 Microcontroller Reference Manual, Rev. 5

9-40 Freescale Semiconductor

If priority levels are not unique, the highest (channel/group) priority that has an active request will be

selected, but the lowest numbered (channel/group) with that priority will be selected by arbitration and

executed by the eDMA engine. The hardware service request handshake signals, error interrupts and error

reporting will be associated with the selected channel.

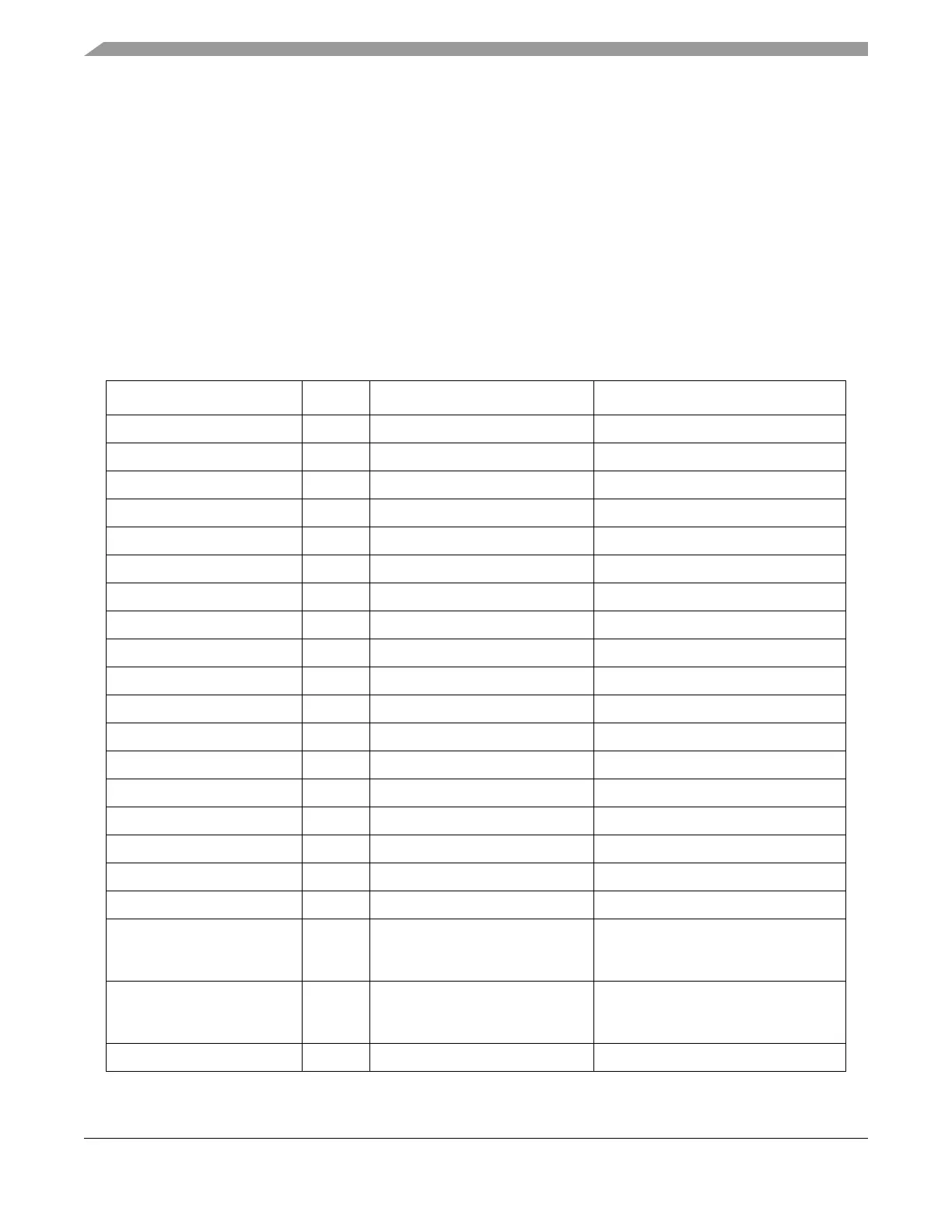

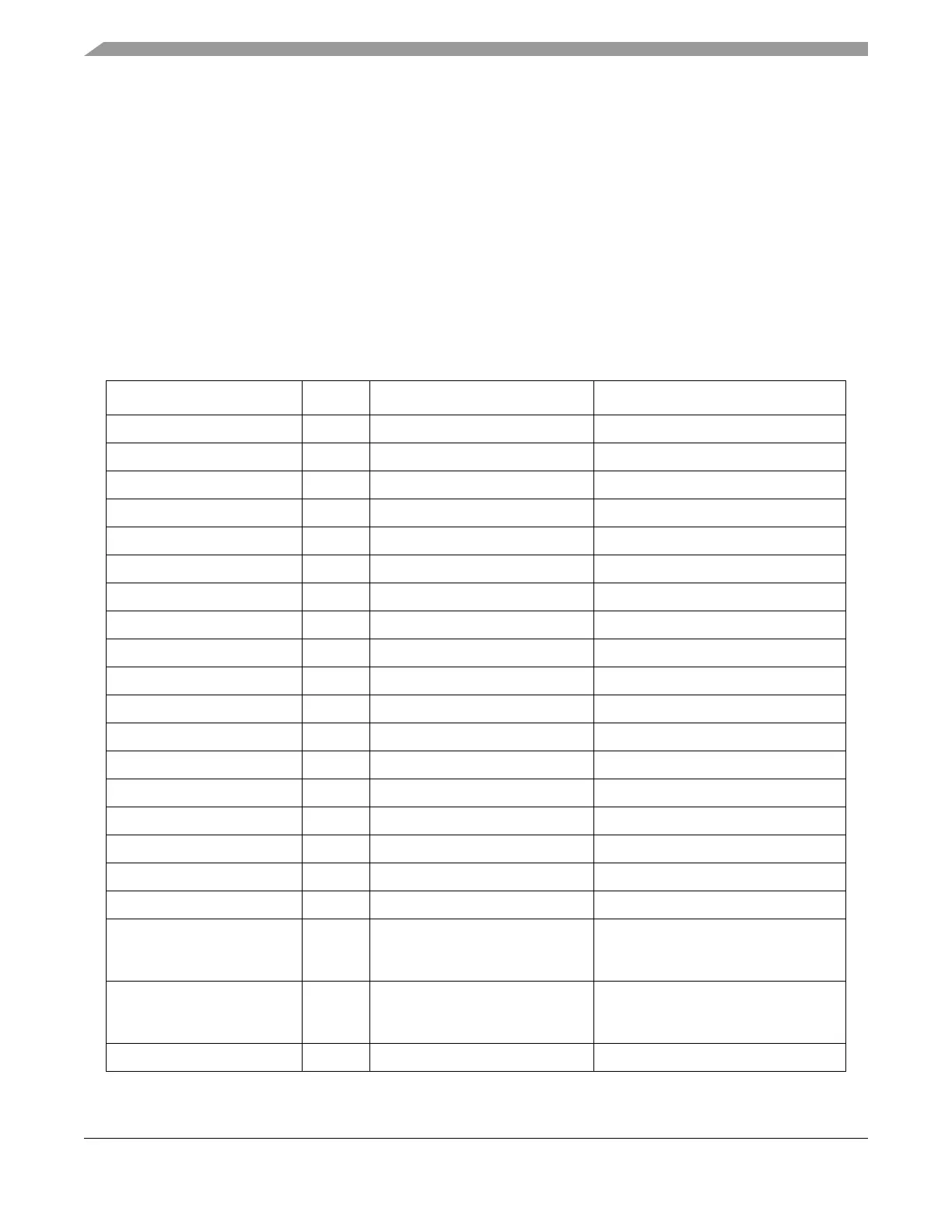

9.5.3 DMA Request Assignments

The assignments between the DMA requests from the modules to the channels of the eDMA are shown in

Table 9-22. The source column is written in C language syntax. The syntax is

module_instance.register[bit].

Note that the MPC5554 has 64 channels but the MPC5553 has 32 channels, and in Table 9-22 channels

0-31 function for both the MPC5553/MPC5554, but only channels 32-63 function for the MPC5554.

Table 9-22. DMA Request Summary for eDMA

DMA Request Channel Source Description

eQADC_FISR0_CFFF0 0 EQADC.FISR0[CFFF0] eQADC Command FIFO 0 Fill Flag

eQADC_FISR0_RFDF0 1 EQADC.FISR0[RFDF0] eQADC Receive FIFO 0 Drain Flag

eQADC_FISR1_CFFF1 2 EQADC.FISR1[CFFF1] eQADC Command FIFO 1 Fill Flag

eQADC_FISR1_RFDF1 3 EQADC.FISR1[RFDF1] eQADC Receive FIFO 1 Drain Flag

eQADC_FISR2_CFFF2 4 EQADC.FISR2[CFFF2] eQADC Command FIFO 2 Fill Flag

eQADC_FISR2_RFDF2 5 EQADC.FISR2[RFDF2] eQADC Receive FIFO 2 Drain Flag

eQADC_FISR3_CFFF3 6 EQADC.FISR3[CFFF3] eQADC Command FIFO 3 Fill Flag

eQADC_FISR3_RFDF3 7 EQADC.FISR3[RFDF3] eQADC Receive FIFO 3 Drain Flag

eQADC_FISR4_CFFF4 8 EQADC.FISR4[CFFF4] eQADC Command FIFO 4 Fill Flag

eQADC_FISR4_RFDF4 9 EQADC.FISR4[RFDF4] eQADC Receive FIFO 4 Drain Flag

eQADC_FISR5_CFFF5 10 EQADC.FISR5[CFFF5] eQADC Command FIFO 5 Fill Flag

eQADC_FISR5_RFDF5 11 EQADC.FISR5[RFDF5] eQADC Receive FIFO 5 Drain Flag

DSPIB_SR_TFFF 12 DSPIB.SR[TFFF] DSPIB Transmit FIFO Fill Flag

DSPIB_SR_RFDF 13 DSPIB.SR[RFDF] DSPIB Receive FIFO Drain Flag

DSPIC_SR_TFFF 14 DSPIC.SR[TFFF] DSPIC Transmit FIFO Fill Flag

DSPIC_SR_RFDF 15 DSPIC.SR[RFDF] DSPIC Receive FIFO Drain Flag

DSPID_SR_TFFF 16 DSPID.SR[TFFF] DSPID Transmit FIFO Fill Flag

DSPID_SR_RFDF 17 DSPID.SR[RFDF] DSPID Receive FIFO Drain Flag

eSCIA_COMBTX 18 ESCIA.SR[TDRE] ||

ESCIA.SR[TC] ||

ESCIA.SR[TXRDY]

eSCIA combined DMA request of the

Transmit Data Register Empty and LIN

Transmit Data Ready DMA requests

eSCIA_COMBRX 19 ESCIA.SR[RDRF] ||

ESCIA.SR[RXRDY]

eSCIA combined DMA request of the

Receive Data Register Full and LIN

Receive Data Ready DMA requests

eMIOS_GFR_F0 20 EMIOS.GFR[F0] eMIOS channel 0 Flag

Loading...

Loading...