MPC5553/MPC5554 Microcontroller Reference Manual, Rev. 5

Freescale Semiconductor 18-11

for motor control. Refer to Section 17.2.1.2, “Output Disable Input—eMIOS Output Disable Input

Signals,” for more information.

18.3.2 Detailed Signal Description

18.3.2.1 Output and Input Channel Signals

The channel signal connections for eTPU engine A (in both the MPC5553 and the MPC5554) and eTPU

engine B (only in the MPC5554) are described in Table 18-1 and Table 18-2, respectively. Each eTPU

channel has an input and output associated with it. In Table 18-1 and Table 18-2 this is represented by the

Input/output column. The eTPU channels can be connected to external pins or wired internally to other

peripheral devices. In the MPC5553/MPC5554, some of the eTPU channels are connected to pins. The pin

connections are represented by the Pin Number column in Table 18-1 and Table 18-2. To the right of the

Pin Number column is the eTPU Channel Connections column that shows the channel number that

corresponds to each input or output pin. Many of these pins are multipurpose, that is they are multiplexed.

Table 18-1 and Table 18-2 shows the other non-eTPU signals listed in the Signals with Which eTPU Signal

is Shared column.

To reduce the number of pins required by the MPC5553/MPC5554’s eTPU while still maintaining the

eTPU’s functionality, the eTPU is also internally wired to the DSPI (20.1, “Introduction”). The DSPI

connections are shown in the column labeled DSPI Serial Channel Connections in Table 18-1 and

Table 18-2. The eTPU microcode may be programmed to set the output level of an eTPU channel in one

of two manners:

• By forcing the logic level to a specified value

• By specifying the logic level output action when a match or transition event occurs

Every eTPU channel input has a digital filter. This filter is designed to filter out noise pulses that have

width less than a specified value. This prevents small noise glitches from being recognized by the

transition detect logic. Any pulses wider than the specified filter width will be passed to the channel

transition detect logic.

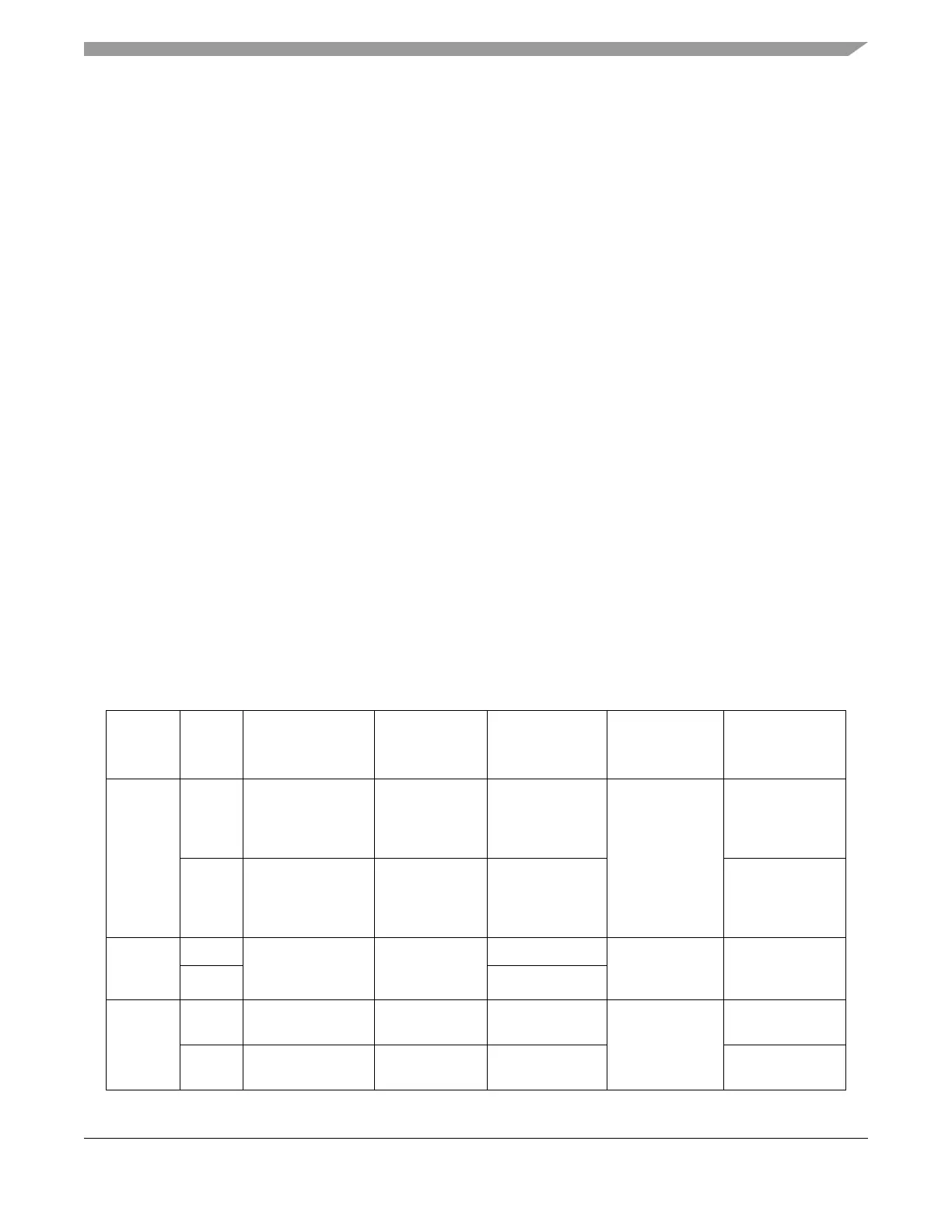

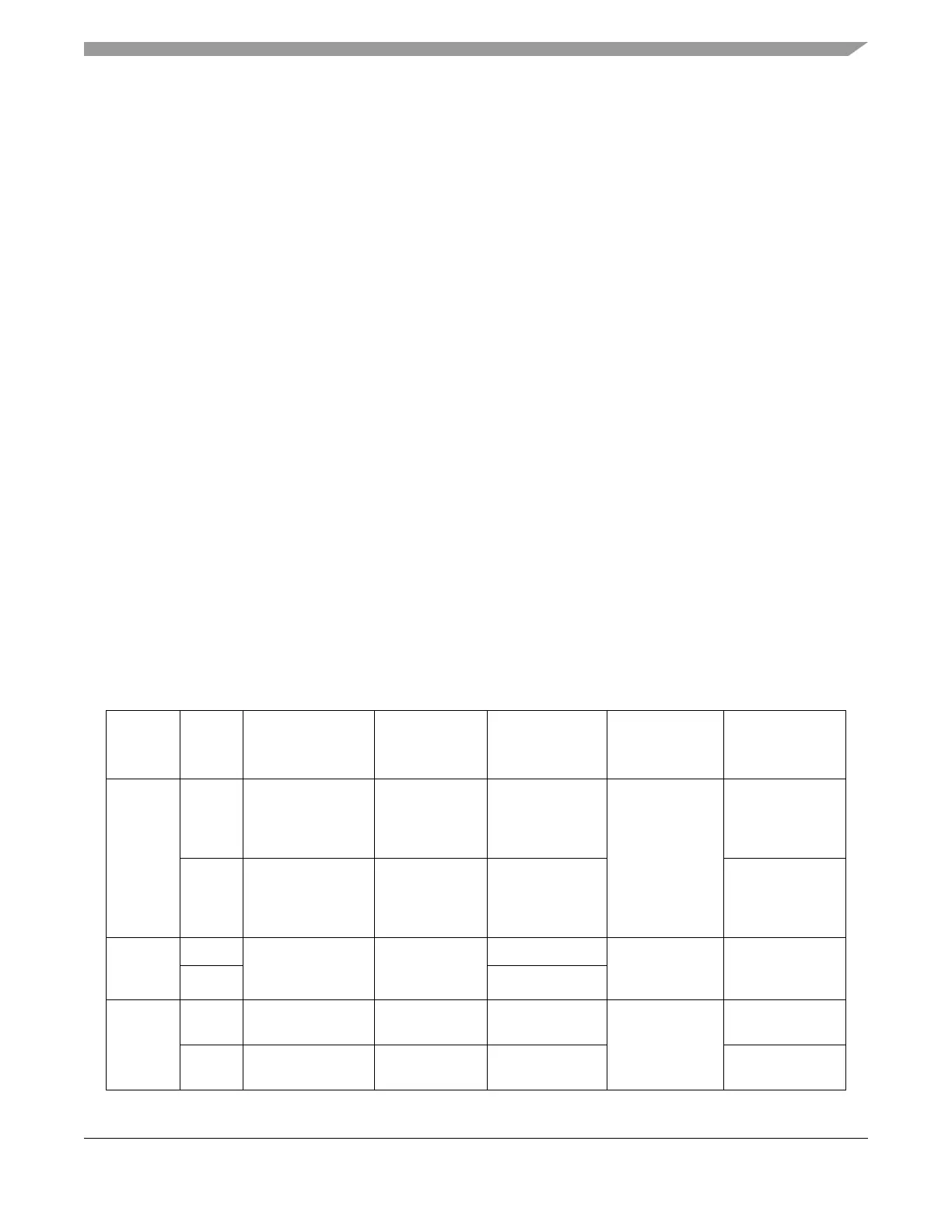

Table 18-1. eTPU A Channel Connection Table (both MPC5553 and MPC5554)

eTPU

Channel

Number

I/O Pin Number

eTPU Channel

Connections

DSPI Serial

Channel

Connections

eTPU A

Signal

Signals with

Which eTPU

Signal is Shared:

0-9 I N3

M4–M1

1

L4–L1

1

K4

0

1–4

5–8

9

not connected

eTPU_A[0:9]

eTPU_A[12:21]

(output only)

GPIO[114:123]

O AF15, AE15, AC16,

AD15, AF16, AE16,

AD16, AF17, AC17,

AE17

0–9 DSPI_C[4:13] eMIOS[0:9]

GPIO[179:188]

10–11 I K3–K2

1

10–11 not connected

eTPU_A[10:11]

eTPU_A[22:23]

(output only)

GPIO[124:125]

O DSPI_C[14:15]

12–15 I K1

J4–J2

1

12

13–15

not connected

eTPU_A[12:15]

GPIO[126:129]

ON3

M4–M2

1

12

13–15

DSPI_C[0:3] eTPU_A[0:3]

GPIO[114:117]

Loading...

Loading...