MPC5553/MPC5554 Microcontroller Reference Manual, Rev. 5

8-2 Freescale Semiconductor

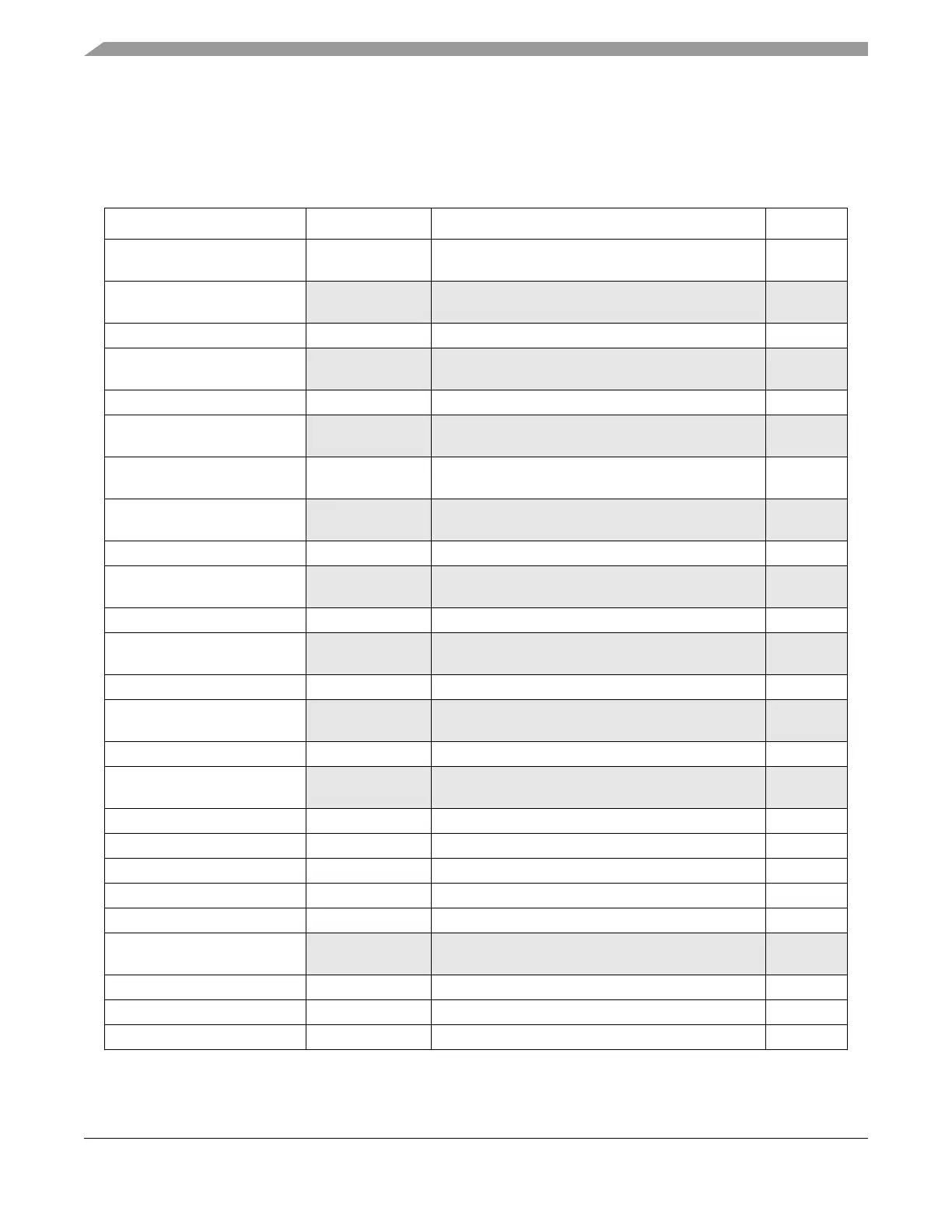

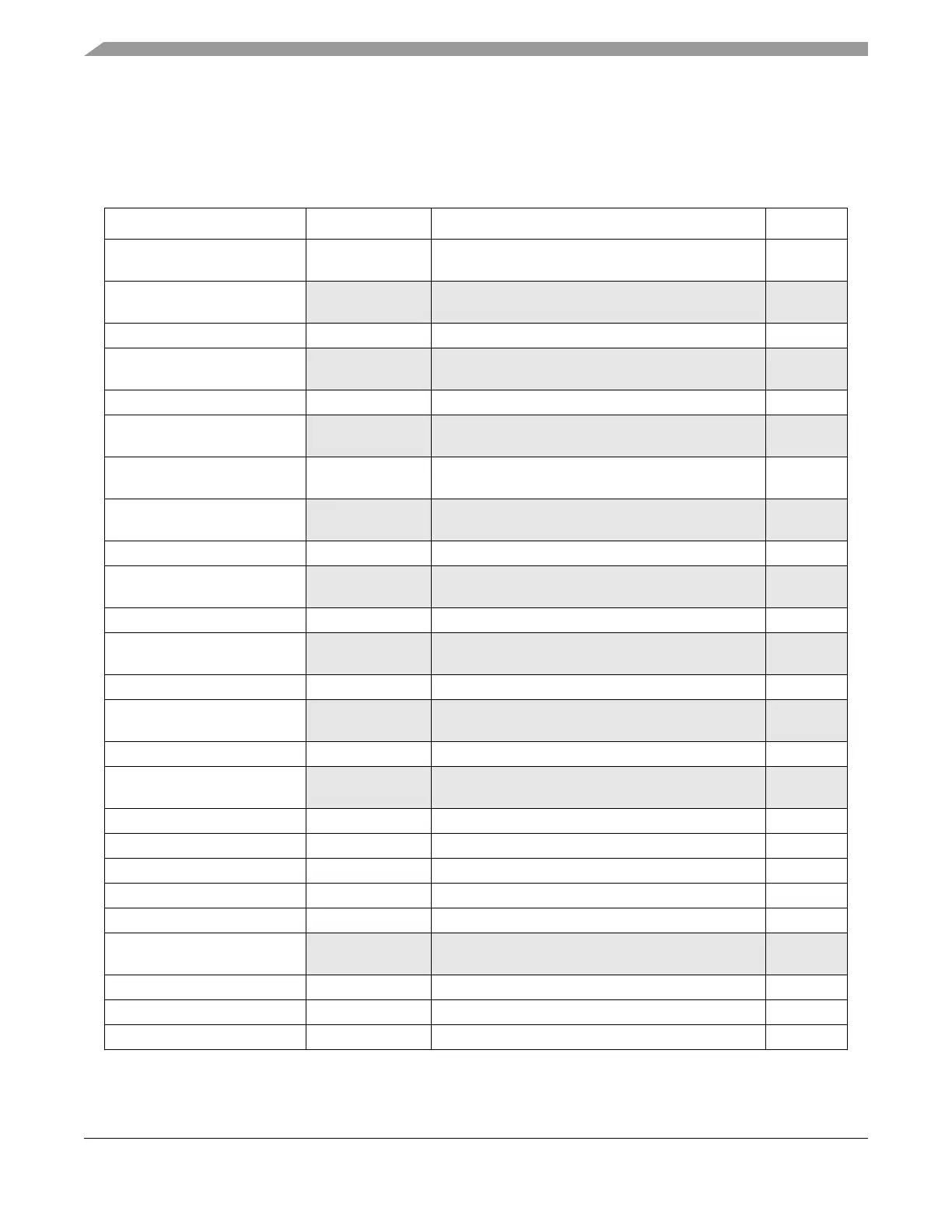

8.2 Memory Map/Register Definition

This section details the programming model for the ECSM. Table 8-1 is the memory map for the ECSM

registers.

Table 8-2. ECSM Memory Map

Address Register Name Register Description Size (bits)

Base (0xFFF4_0000)

+ 0x016

ECSM_SWTCR Software watchdog timer control register

1

16

Base + 0x0018–

Base + 0x001A

— Reserved —

Base + 0x001B ECSM_SWTSR Software watchdog timer service register

1

8

Base + 0x001C–

Base + 0x001E

— Reserved —

Base + 0x01F ECSM_SWTIR Software watchdog timer interrupt register

1

8

Base + 0x0020–

Base + 0x0023

— Reserved —

Base (0xFFF4_0000) +

0x0024–Base + 0x0027

FBOMCR FEC Burst Optimization Master Control Register

(MPC5553 Only)

32

Base + 0x0028–

Base + 0x0042

— Reserved —

Base (0xFFF4_0000) + 0x0043 ECSM_ECR ECC configuration register 8

Base + 0x0044–

Base + 0x0046

— Reserved —

Base + 0x0047 ECSM_ESR ECC status register 8

Base + 0x0048–

Base + 0x0049

— Reserved —

Base + 0x004A ECSM_EEGR ECC error generation register 16

Base + 0x004B–

Base + 0x004F

— Reserved —

Base + 0x0050 ECSM_FEAR Flash ECC address register 32

Base + 0x0054–

Base + 0x0055

— Reserved —

Base + 0x0056 ECSM_FEMR Flash ECC master register 8

Base + 0x0057

ECSM_FEAT Flash ECC attribute register 8

Base + 0x0058 ECSM_FEDRH Flash ECC data high register 32

Base + 0x005C ECSM_FEDRL Flash ECC data low register 32

Base + 0x0060

ECSM_REAR RAM ECC address register 32

Base + 0x0064–

Base + 0x0065

— Reserved —

Base + 0x0066 ECSM_REMR RAM ECC master register 8

Base + 0x0067

ECSM_REAT RAM ECC attributes register 8

Base + 0x0068 ECSM_REDRH RAM ECC data high register 32

Loading...

Loading...