MPC5553/MPC5554 Microcontroller Reference Manual, Rev. 5

5-4 Freescale Semiconductor

5.2 External Signal Description

The PBRIDGE has no external signals.

5.3 Memory Map/Register Definition

The memory maps for the 32-bit PBRIDGE registers are shown in Table 5-2 and Table 5-3.

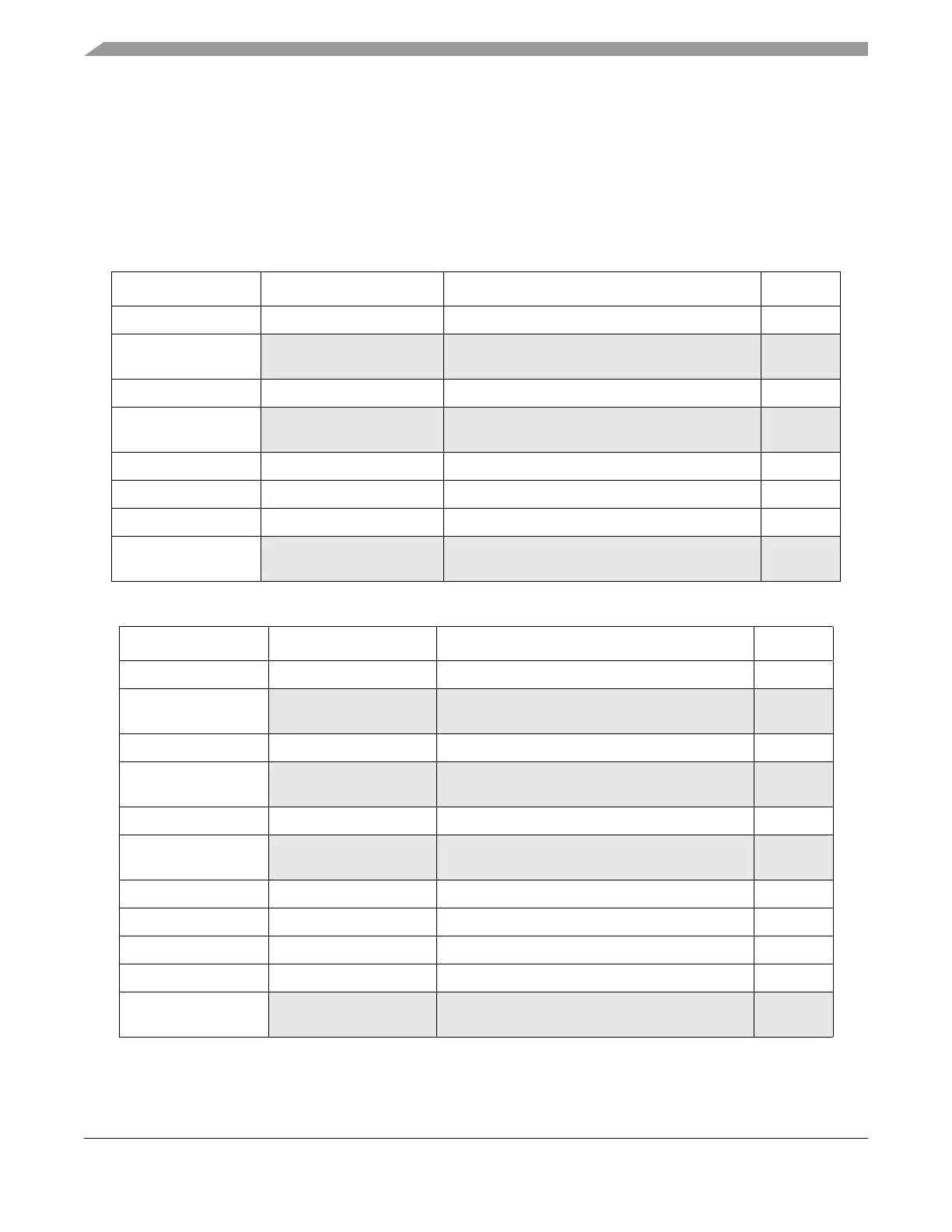

Table 5-2. PBRIDGE_A Memory Map

Address Register Name Register Description Size (bits)

Base (0xC3F0_0000) PBRIDGE_A_MPCR Master privilege control register 32

Base + 0x0004–

Base + 0x001F

— Reserved —

Base + 0x0020 PBRIDGE_A_PACR0 Peripheral access control register 0 32

Base + 0x0024–

Base + 0x003F

— Reserved —

Base + 0x0040 PBRIDGE_A_OPACR0 Off-platform peripheral access control register 0 32

Base + 0x0044 PBRIDGE_A_OPACR1 Off-platform peripheral access control register 1 32

Base + 0x0048 PBRIDGE_A_OPACR2 Off-platform peripheral access control register 2 32

Base + 0x004C–

Base + 0x0053

— Reserved —

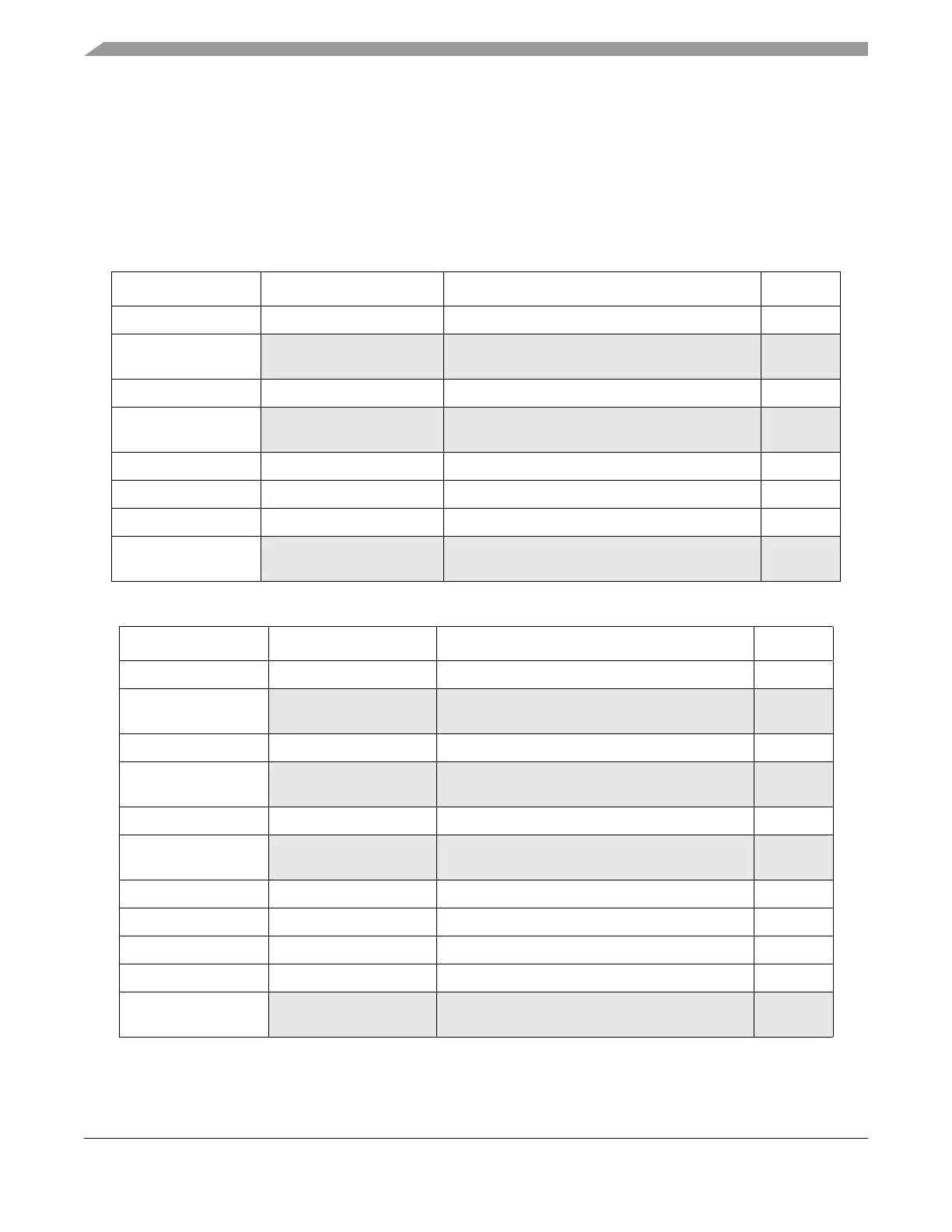

Table 5-3. PBRIDGE_B Memory Map

Address Register Name Register Description Size (bits)

Base (0xFFF0_0000) PBRIDGE_B_MPCR Master privilege control register 32

Base + 0x0004–

Base + 0x001F

— Reserved —

Base + 0x0020 PBRIDGE_B_PACR0 Peripheral access control register 0 32

Base + 0x0024–

Base + 0x0027

— Reserved —

Base + 0x028 PBRIDGE_B_PACR2 Peripheral access control register 2 32

Base + 0x002C–

Base + 0x003F

— Reserved —

Base + 0x0040 PBRIDGE_B_OPACR0 Off-platform peripheral access control register 0 32

Base + 0x0044 PBRIDGE_B_OPACR1 Off-platform peripheral access control register 1 32

Base + 0x0048 PBRIDGE_B_OPACR2 Off-platform peripheral access control register 2 32

Base + 0x004C PBRIDGE_B_OPACR3 Off-platform peripheral access control register 3 32

Base + 0x0050–

Base + 0x0053

— Reserved —

Loading...

Loading...