MPC5553/MPC5554 Microcontroller Reference Manual, Rev. 5

Freescale Semiconductor 8-15

8.3 Initialization/Application Information

In order to use the ECC mechanism for internal SRAM accesses, it is essential for the ECC check bits to

be initialized after power on. See Section 15.7, “Initialization/Application Information.”

All non-correctable ECC errors cause a data storage interrupt (IVOR2) regardless of whether

non-correctable reporting is enabled. A data storage interrupt handler can determine:

— The destination location asserted an error, the ESR[XTE] bit will be set.

— The address where the error occurred, using the data exception address register (DEAR).

However, details of the ECC error are not reported unless non-correctable reporting is enabled by setting

bits ERNCR and EFNCR in the ECSM_ECR. When these bits are set and a non-correctable ECC error

occurs, error information is recorded in other ECSM registers and an interrupt request is generated on

vector 9 of the INTC. If properly enabled, this INTC vector 9 can cause an external interrupt (IVOR4)

along with the data storage interrupt (IVOR2).

To avoid the external interrupt (IVOR4) being generated, the application enables non-correctable reporting

in the ECSM, but does not enable that its interrupt be recognized. The INTC_PSR[PRI] value for the ECC

error interrupt request is left at its reset value of 0. The 0 priority level is the lowest priority and is never

recognized, resulting in only the data storage interrupt (IVOR2) being taken.

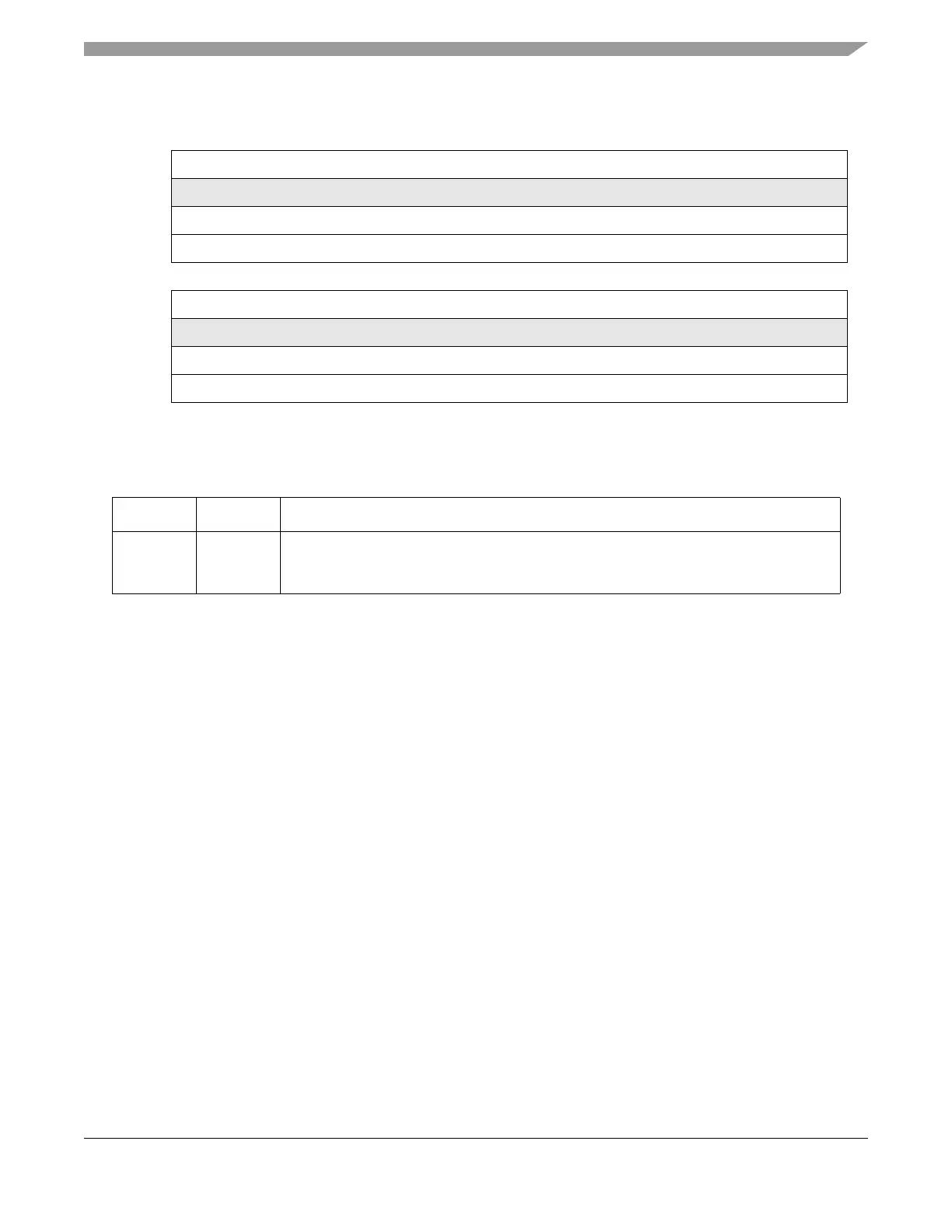

0123456789101112131415

RREDL

W

ResetUUUUUUUUUUUUUUUU

Reg Addr ECSM Base + 0x006C

16 17 18 19 20 21 22 23 24 25 26 27 28 29 30 31

RREDL

W

ResetUUUUUUUUUUUUUUUU

Reg Addr ECSM Base + 0x006C

1

“U” signifies a bit that is uninitialized.

Figure 8-13. RAM ECC Data Low Register (ECSM_REDRL)

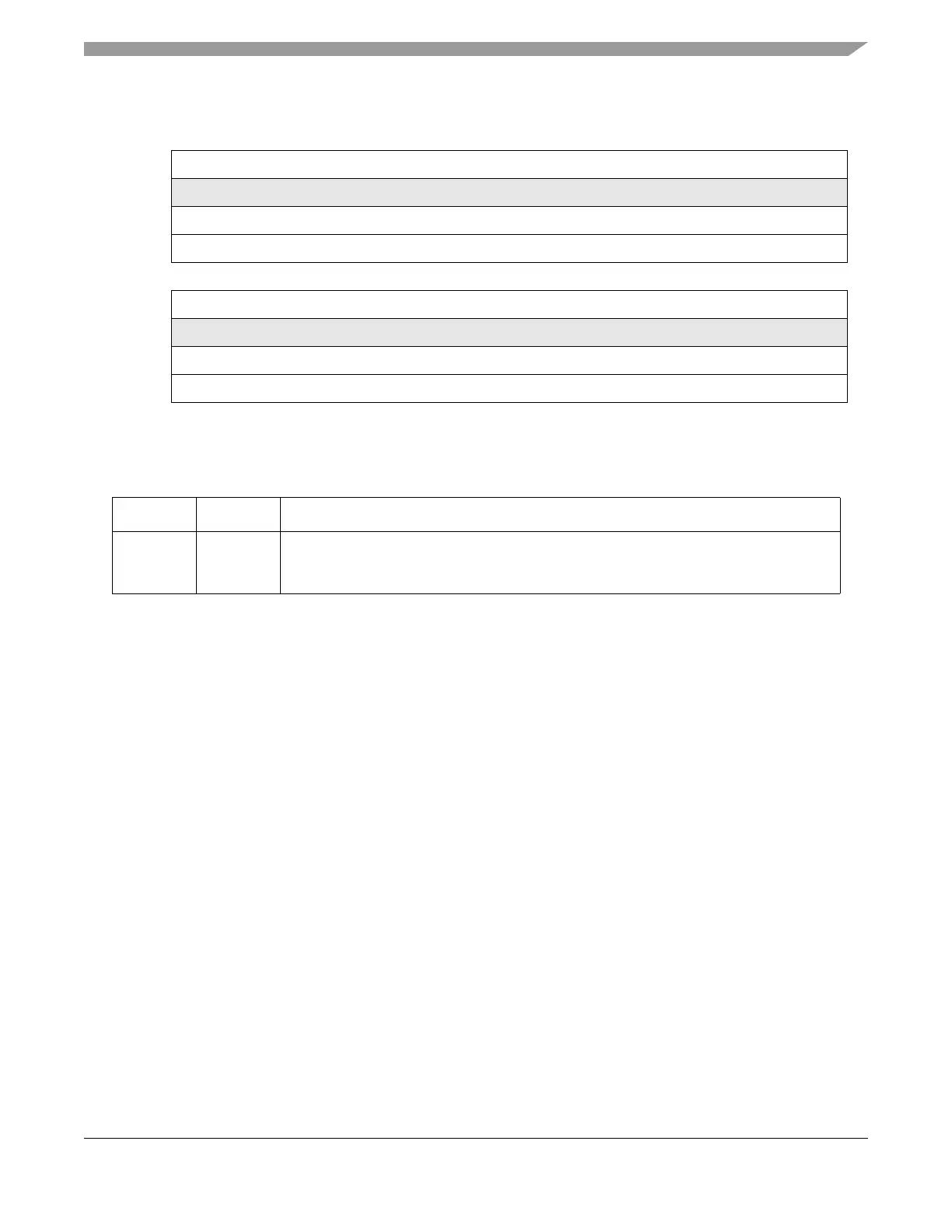

Table 8-15. ECSM_REDRL Field Descriptions

Bits Name Description

0–31 REDL

[0:31]

RAM ECC data. Contains the data associated with the faulting access of the last,

properly-enabled RAM ECC event. The register contains the data value taken directly from

the data bus. The reset value of this field is undefined.

Loading...

Loading...