MPC5553/MPC5554 Microcontroller Reference Manual, Rev. 5

Freescale Semiconductor 8-7

8.2.1.6 Flash ECC Address Register (ECSM_FEAR)

The ECSM_FEAR is a 32-bit register for capturing the address of the last, properly-enabled ECC event in

the flash memory. Depending on the state of the ECSM_ECR, an ECC event in the flash causes the

address, attributes and data associated with the access to be loaded into the ECSM_FEAR, ECSM_FEMR,

ECSM_FEAT, and ECSM_FEDR registers, and the appropriate flag (F1BC or FNCE) in the ECSM_ESR

to be asserted.

The address that is captured in ECSM_FEAR is the flash page address as seen on the system bus. Refer to

Section 13.3.2.7, “Address Register (FLASH_AR)” to retrieve the doubleword address.

8—Reserved

9–15 ERRBIT Error bit position. Defines the bit position which is complemented to create the data

error on the write operation. The bit specified by this field plus the odd parity bit of the

ECC code are inverted.

The internal SRAM controller follows a vector bit ordering scheme where LSB=0.

Errors in the ECC syndrome bits can be generated by setting this field to a value

greater than the internal SRAM width. The following association between the ERRBIT

field and the corrupted memory bit is defined:

if ERRBIT = 0, then RAM[0] is inverted

if ERRBIT = 1, then RAM[1] is inverted

...

if ERRBIT = 63, then RAM[63] is inverted

if ERRBIT = 64, then ECC Parity[0] is inverted

if ERRBIT = 65, then ECC Parity[1] is inverted

...

if ERRBIT = 71, then ECC Parity[7] is inverted

For ERRBIT values greater than 71, no bit position is inverted.

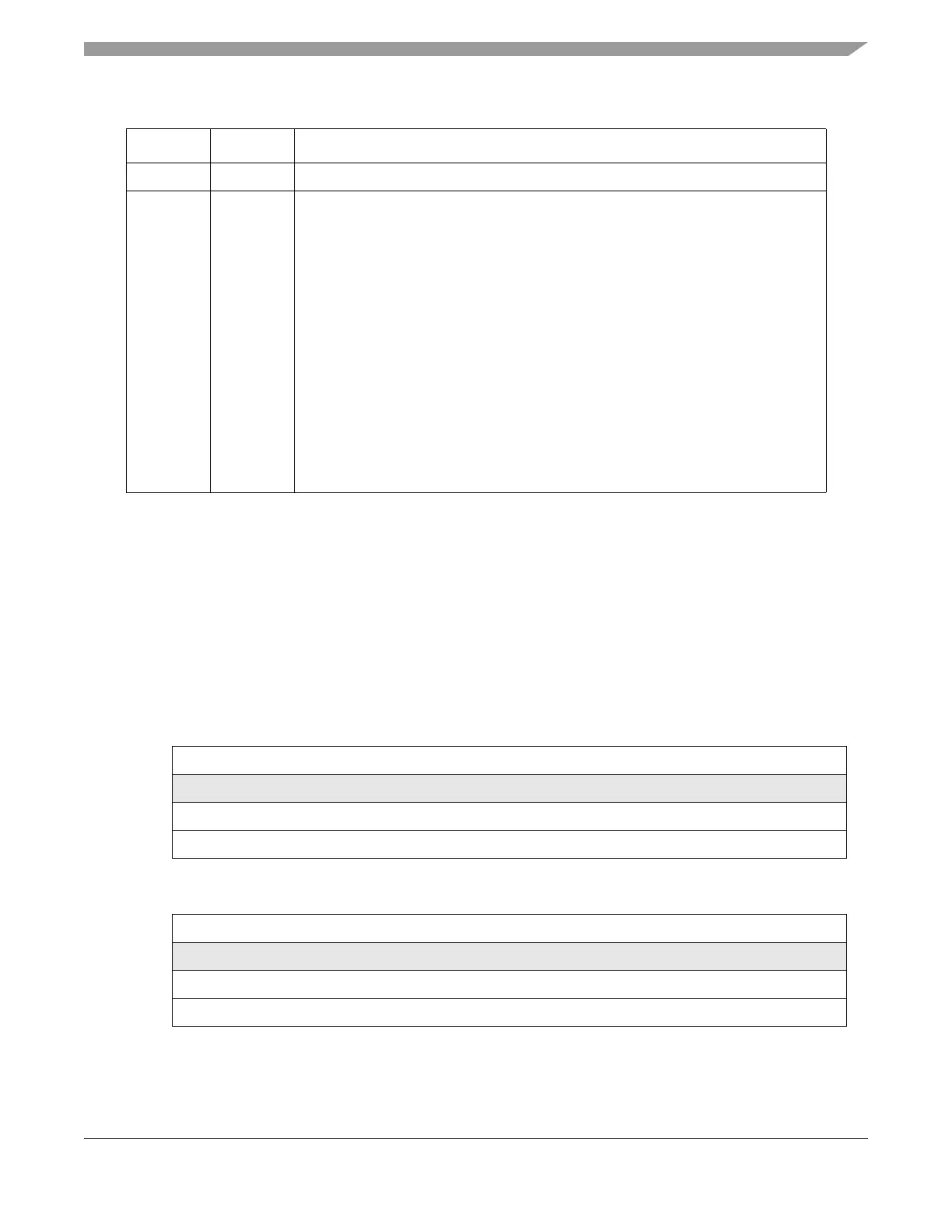

0123456789101112131415

R FEAR

W

ResetUUUUUUUUUUUUUUUU

Reg Addr Base + 0x0050

16 17 18 19 20 21 22 23 24 25 26 27 28 29 30 31

R FEAR

W

ResetUUUUUUUUUUUUUUUU

Reg Addr Base + 0x0050

1

“U” signifies a bit that is uninitialized.

Figure 8-4. Flash ECC Address Register (ECSM_FEAR)

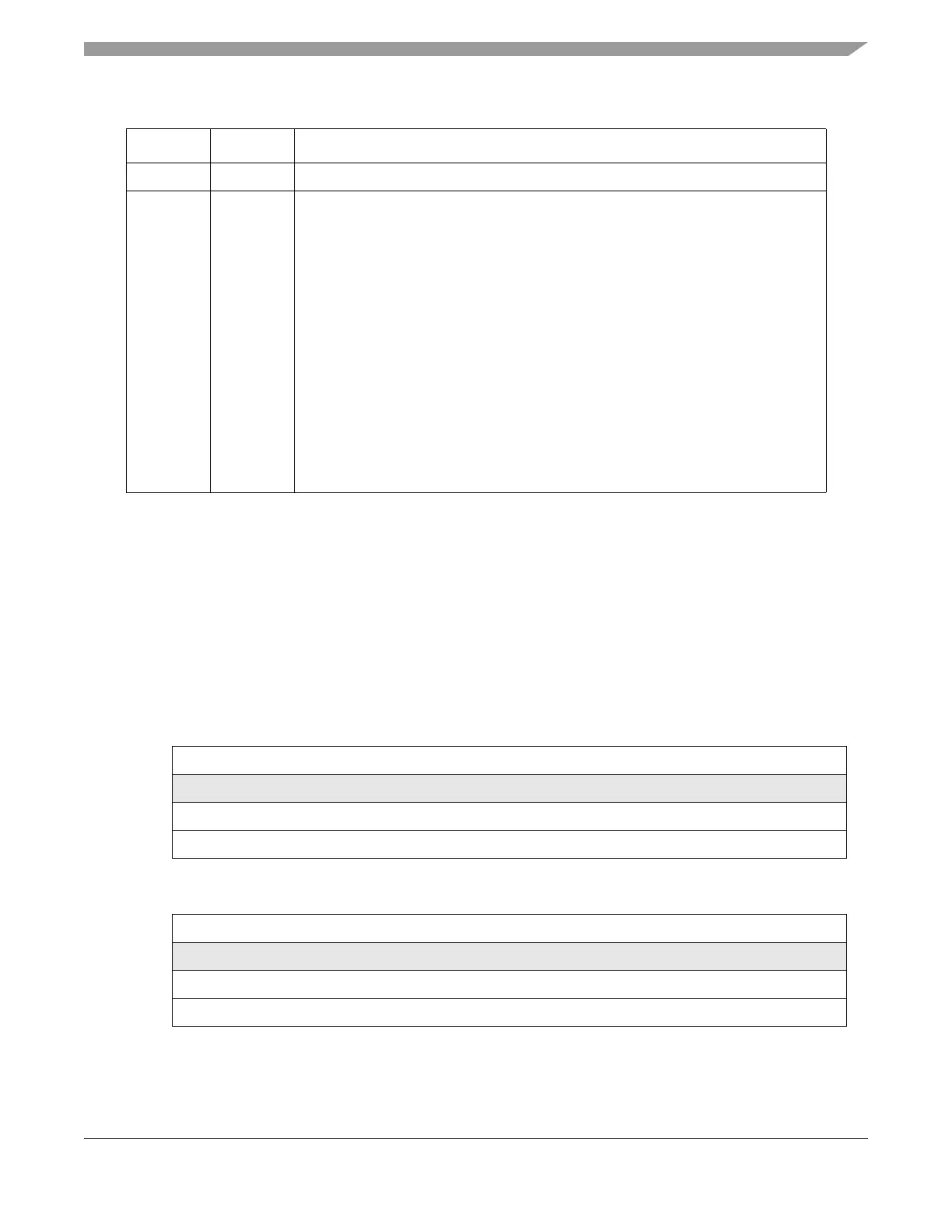

Table 8-5. ECSM_EEGR Field Definitions (Continued)

Bits Name Description

Loading...

Loading...