MPC5553/MPC5554 Microcontroller Reference Manual, Rev. 5

13-36 Freescale Semiconductor

13.4.2.6.4 External Boot Default

The SIU latches the boot default value in the SIU_RSR BOOTCFG[0:1] bits if and only if RSTCFG is

negated. Censorship logic sets the boot default value before the SIU latches the value to

external-with-external-master access disabled (EXTM=0) if the lower half of the censorship control word

equals 0xFFFF or 0x0000. Otherwise, censorship logic sets the boot default value to internal flash.

13.4.3 Flash Memory Array: Stop Mode

Stop mode is entered by setting the FLASH_MCR[STOP] bit. The FLASH_MCR[STOP] bit cannot be

written when FLASH_MCR[PGM] = 1 or FLASH_MCR[ERS] = 1. In stop mode all DC current sources

in the flash module are disabled. Stop mode is exited by clearing the FLASH_MCR[STOP] bit.

Accessing the flash memory array when STOP is asserted results in an error response from the flash BIU

to the system bus. Memory array accesses must not be attempted until the flash transitions out of stop

mode.

13.4.4 Flash Memory Array: Reset

A reset is the highest priority operation for the flash and terminates all other operations.

The flash uses reset to initialize register and status bits to their default reset values. If the flash is executing

a program or erase operation and a reset is issued, the operation will be aborted and the flash will disable

the high voltage logic without damage to the high voltage circuits. Reset aborts all operations and forces

the flash into normal operating mode ready to receive accesses. FLASH_MCR[DONE] will be set to 1 at

the exit of reset.

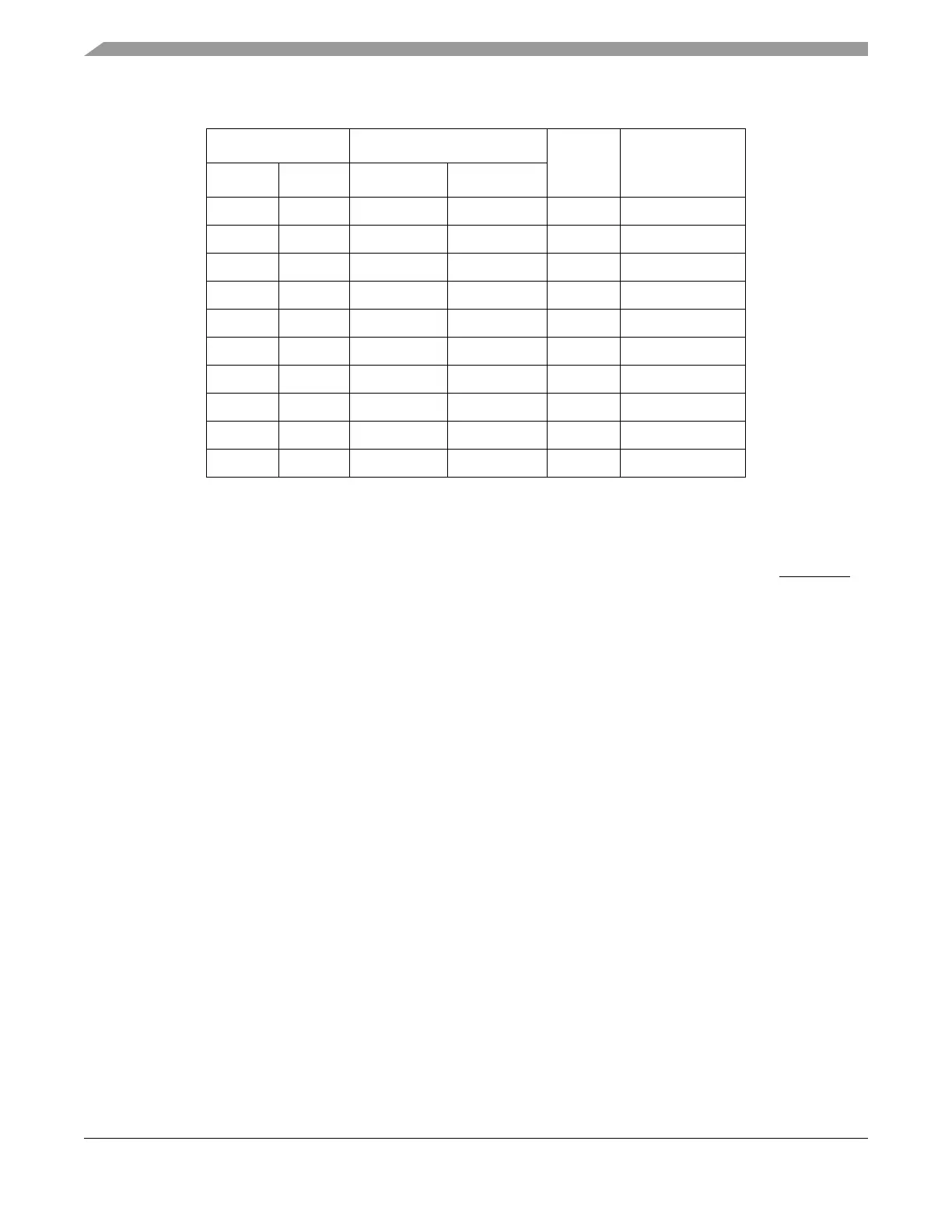

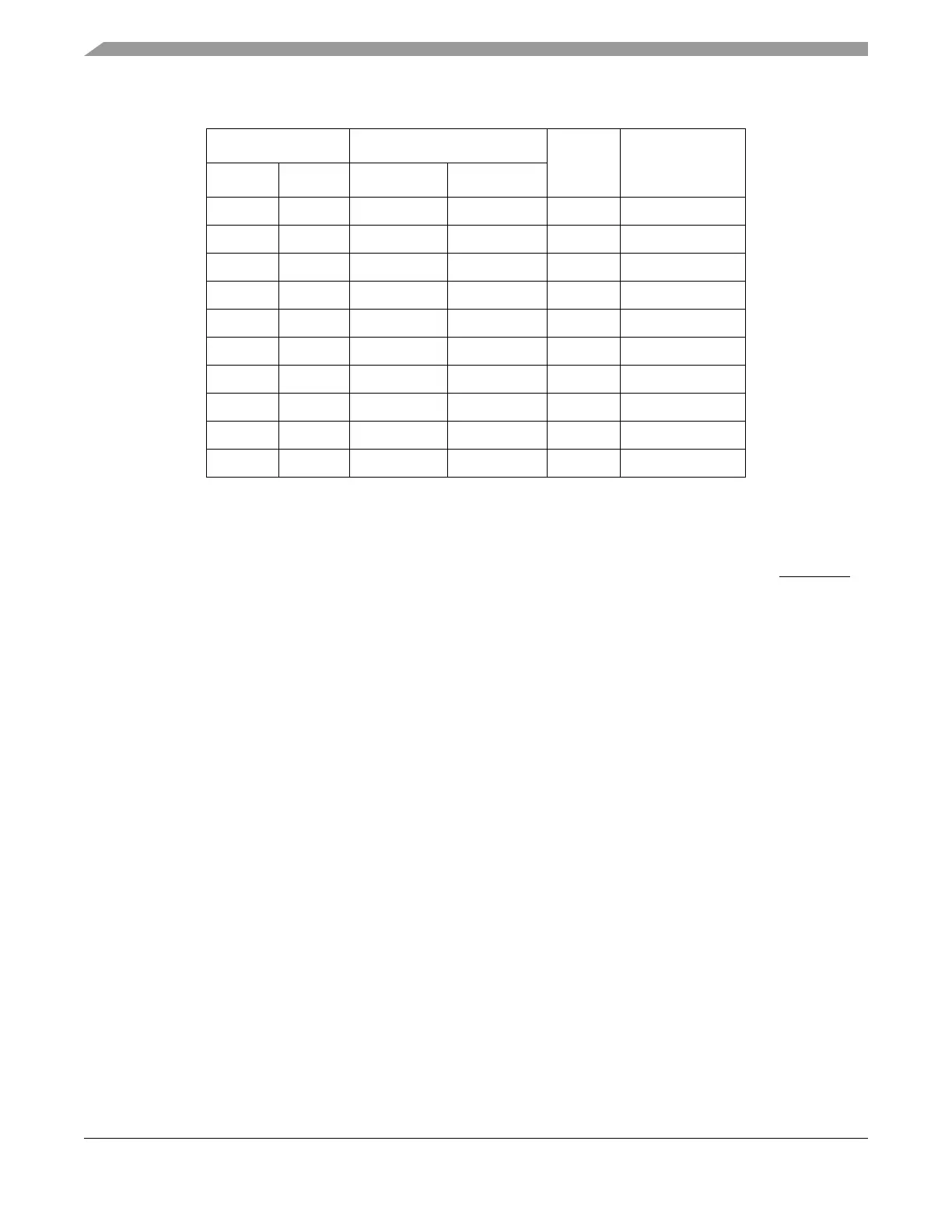

0 1 0xXXXX 0x55AA 0 Yes

0 1 0xXXXX !0x55AA 0 Yes

0 0 0x55AA 0xXXXX 1 Yes

0 0 !0x55AA 0xXXXX 1 No

1 0 0x55AA 0xXXXX 1 Yes

1 0 !0x55AA 0xXXXX 1 No

1 1 0x55AA 0xXXXX 1 Yes

1 1 !0x55AA 0xXXXX 1 No

0 1 0xXXXX 0x55AA 1 No

0 1 0xXXXX !0x55AA 1 No

1

BOOTCFG[0:1] bits are located in the SIU_RSR.

2

EXTM bit is located in the EBI_MCR.

Table 13-18. PFBAPR Modification Logic (Continued)

BOOTCFG

1

Censorship Control Word

EXTM

2

PFBAPR Bitfields

Writable

[0] [1] Upper Half Lower Half

Loading...

Loading...