MPC5553/MPC5554 Microcontroller Reference Manual, Rev. 5

Freescale Semiconductor 12-3

12.1.2 Overview

The EBI includes a memory controller that generates interface signals to support a variety of external

memories. This includes single data rate (SDR) burst mode flash, external SRAM, and asynchronous

memories. It supports up to four regions (via chip selects), each with its own programmed attributes.

12.1.3 Features

Features include the following:

• 1.8-3.3 V I/O

• 32-bit internal address bus with transfer size indication, but

— 24 bits available as external pins in the MPC5554 and in the MPC5553 416 and 324 BGA

packages

— 20 bits available in the MPC5553 416 and 324 BGA packages

— No external bus in the MPC5553 208 BGA package

— Table 12-1 shows the address bus packages supported.

• The external bus interface and the calibration bus interface share ADDR[12:26]. Refer to

Table 12-1.

• 32-bit data bus available for both external memory accesses and transactions involving an external

master, but

— 32 bits available in the MPC5554 and in the MPC5553 416 BGA package

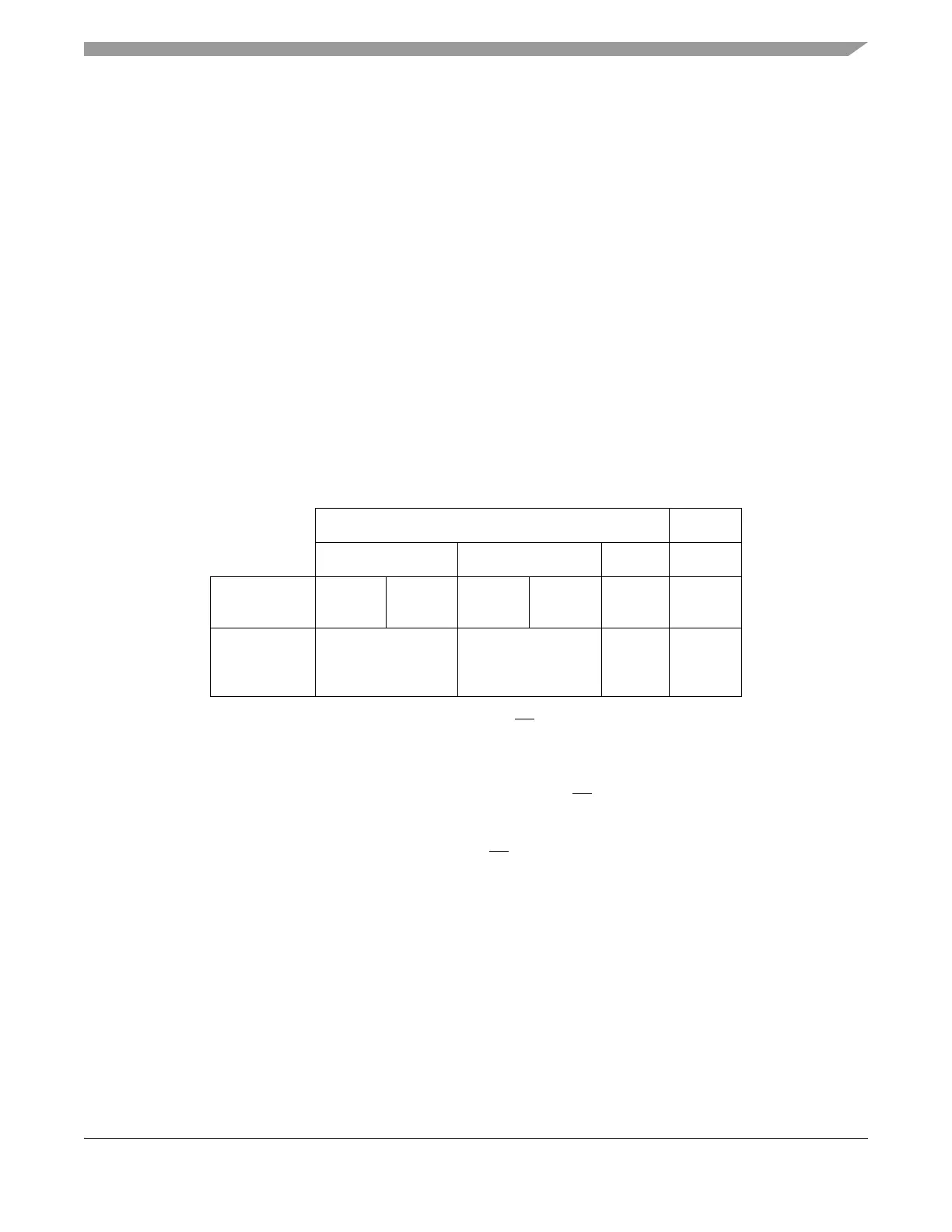

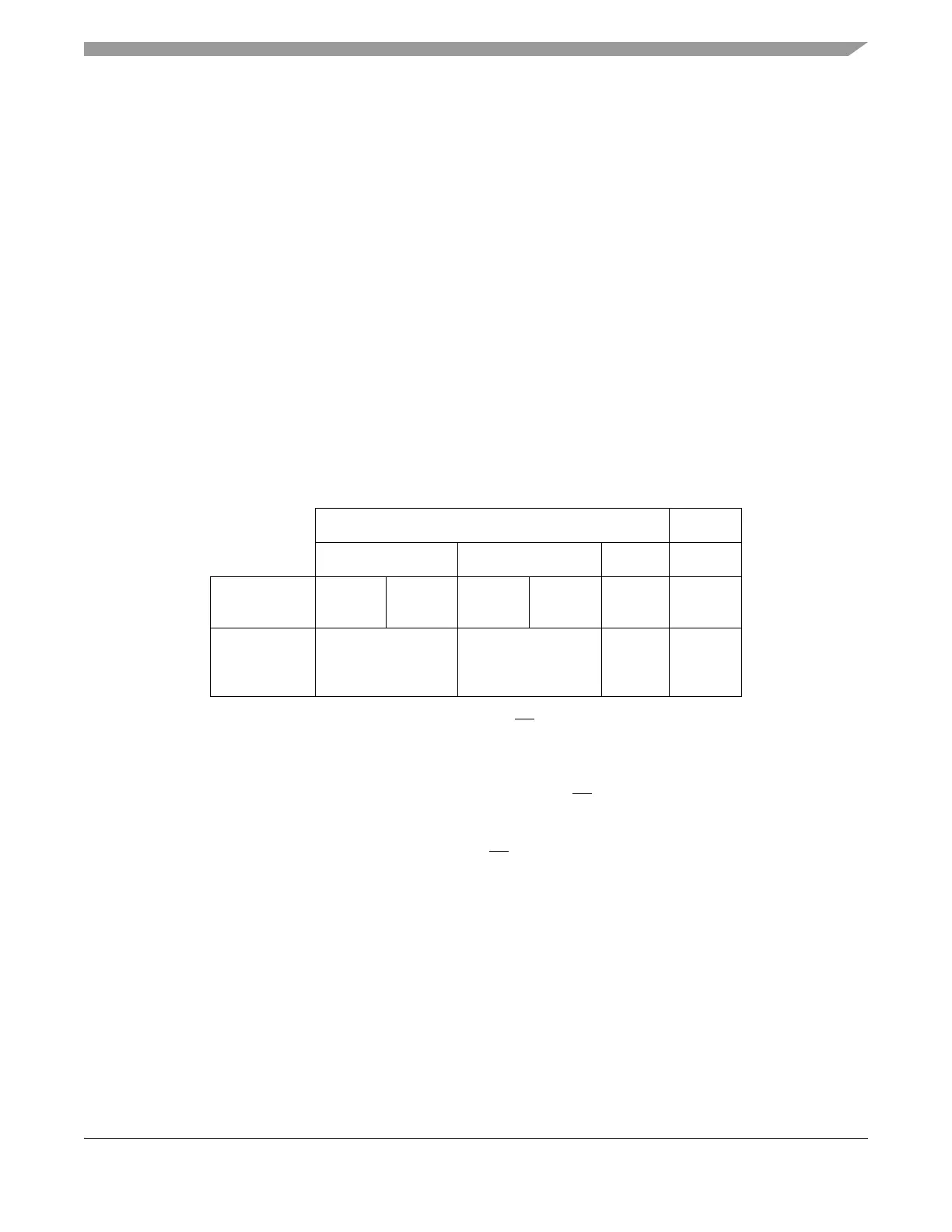

Table 12-1. Address Bus Sizes in MPC5554 and MPC5553

MPC5553 MPC5554

416 324 208 416

EBI Address

Bus Size

24 bit

1

1

24 bits available: ADDR[12:31] is the default pin set, then ADDR[8:11] is added to

make the 24 bits. ADDR[8:11] can be used, or CS[0:3] / ADDR[8:11] can be

configured by PCR to be ADDR[8:11]. Only one set of ADDR[8:11] must be used for

address input, however.

20 bit

2

2

20 bits is default EBI size for the 416 package (ADDR[12:31]).

24 bit

3

3

24 bits available: ADDR[12:31] is the default pin set, then CS[0:3] must be configured

to be ADDR[8:11] in order to have 24 bits.

20 bit

4

4

20 bits is default EBI size for the 324 package (ADDR[12:31])

None 24 bit

5

5

24 bits available: ADDR[8:31] is typical, or CS[0:3] can be configured to be

ADDR[8:11]. Only one set of ADDR[8:11] must be used for address input, however.

Calibration

Address Bus

Size

19 or 21 bits

6

6

The calibration bus interface (CBI) and the external bus interface (EBI) share the

same bus. To use a 21-bit calibration bus, the CBI uses EBI signals ADDR[12:26] and

CAL_ADDR[10:11], and ADDR[8:11] must be configured in the PCR to use

CAL_ADDR[27:30]. When the calibration bus is 19 bits, ADDR[12:26] and

CAL_ADDR[27:30] are used (by configuring ADDR[8:11] in the PCR). Set the PA

field in the SIU_PCR register to 0b1 to use the calibration bus interface or the EBI.

19 or 21 bits

6

None N.A.

Loading...

Loading...