MPC5553/MPC5554 Microcontroller Reference Manual, Rev. 5

Freescale Semiconductor 25-41

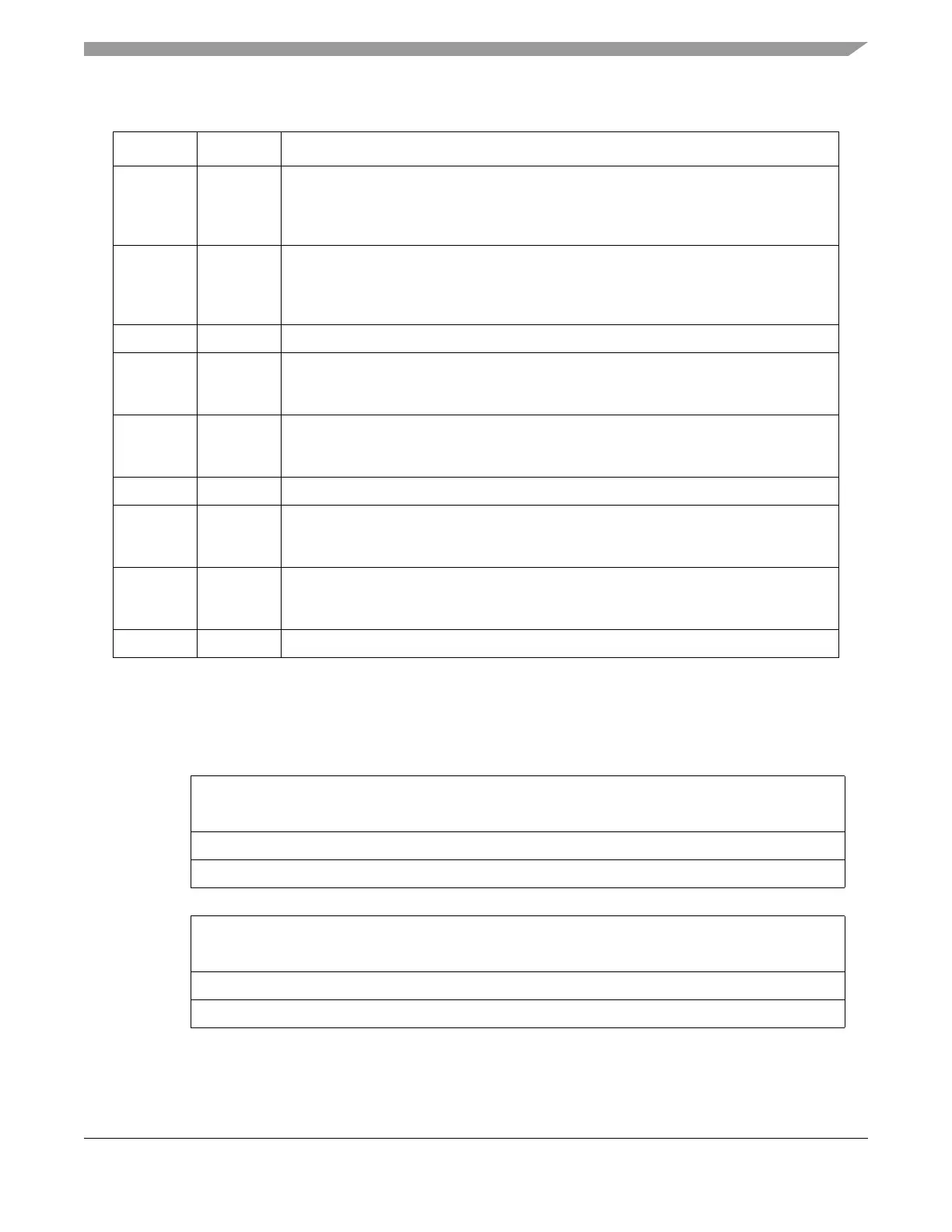

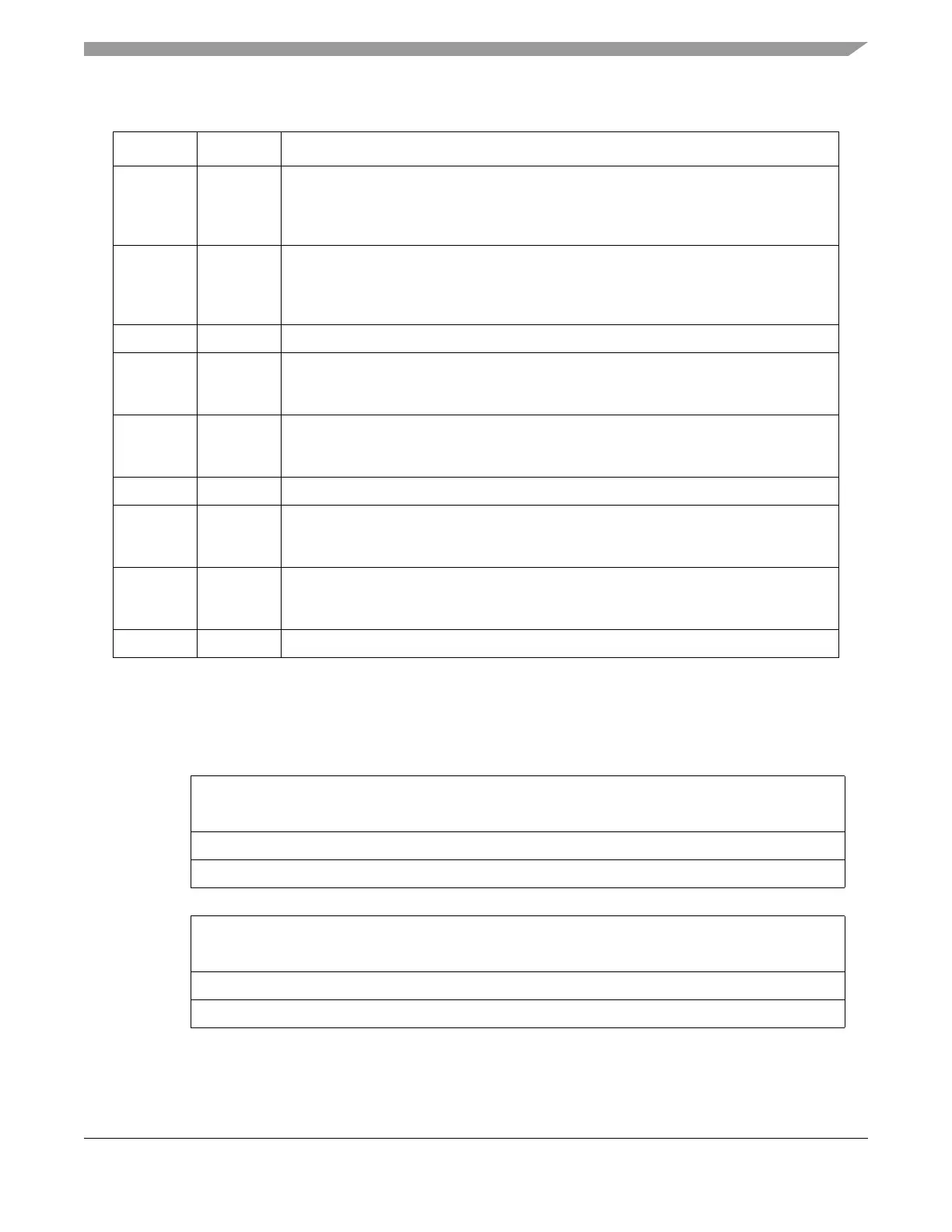

25.11.8 Data Trace Start Address Registers 1 and 2 (DTSAn)

The data trace start address registers define the start addresses for each trace channel.

Table 25-31. DTC Field Description

Bits Name Description

31–30 RWT1

[1:0]

Read/write trace 1.

00 No trace enabled

X1 Enable data read trace

1X Enable data write trace

29–28 RWT2

[1:0]

Read/write trace 2.

00 No trace enabled

X1 Enable data read trace

1X Enable data write trace

27–8 — Reserved.

7 RC1 Range control 1.

0 Condition trace on address within range

1 Condition trace on address outside of range

6 RC2 Range control 2

0 Condition trace on address within range

1 Condition trace on address outside of range

5–4 — Reserved.

3 DI1 Data access/instruction access trace 1.

0 Condition trace on data accesses

1 Condition trace on instruction accesses

2 DI2 Data access/instruction access trace 2

0 Condition trace on data accesses

1 Condition trace on instruction accesses

1–0 — Reserved.

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16

R Data Trace Start Address

W

Reset0000000000000000

Nexus Reg 0xE

1514131211109876543210

R Data Trace Start Address

W

Reset0000000000000000

Nexus Reg 0xE

Figure 25-21. Data Trace Start Address Register 1 (DTSA1)

Loading...

Loading...